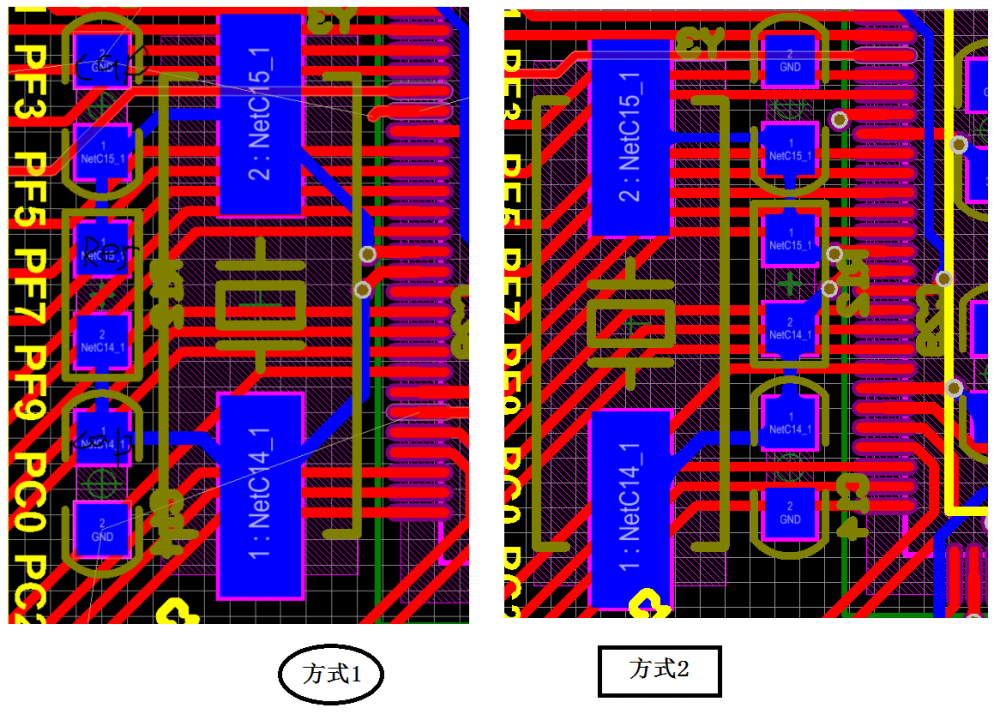

PCB设计上,晶振和外部负载电容之间如何摆放布局最合理?

如下是两种设计案例,哪种好些呢?

| 有奖活动 | |

|---|---|

| 【EEPW电子工程师创研计划】技术变现通道已开启~ | |

| 发原创文章 【每月瓜分千元赏金 凭实力攒钱买好礼~】 | |

| 【EEPW在线】E起听工程师的声音! | |

| “我踩过的那些坑”主题活动——第001期 | |

| 高校联络员开始招募啦!有惊喜!! | |

| 【工程师专属福利】每天30秒,积分轻松拿!EEPW宠粉打卡计划启动! | |

| 送您一块开发板,2025年“我要开发板活动”又开始了! | |

| 打赏了!打赏了!打赏了! | |

| 打赏帖 | |

|---|---|

| 电流检测模块MAX4080S被打赏10分 | |

| 【我踩过的那些坑】calloc和malloc错误使用导致跑飞问题排查被打赏50分 | |

| 多组DCTODC电源方案被打赏50分 | |

| 【我踩过的那些坑】STM32cubeMX软件的使用过程中的“坑”被打赏50分 | |

| 新手必看!C语言精华知识:表驱动法被打赏50分 | |

| 【我踩过的那些坑】杜绑线问题被打赏50分 | |

| 【我踩过的那些坑】STM32的硬件通讯调试过程的“坑”被打赏50分 | |

| 【我踩过的那些坑】晶振使用的问题被打赏100分 | |

| 【我踩过的那些坑】电感选型错误导致的处理器连接不上被打赏50分 | |

| 【我踩过的那些坑】工作那些年踩过的记忆深刻的坑被打赏10分 | |