概述

TI的集成电路和参考设计配有原理图、测试数据和设计文件,可帮助您创建通信有效载荷系统。

设计要求

现代通信有效载荷设计需要:

高带宽 ADC 和 DAC,从而提供数据吞吐量超高的系统。

超低抖动时钟解决方案,从而更大限度提高数据转换器的性能。

面向航天市场的高集成度负载点 (POL) 解决方案,从而减小甚至是超高功耗处理板所需的总体电路板尺寸。

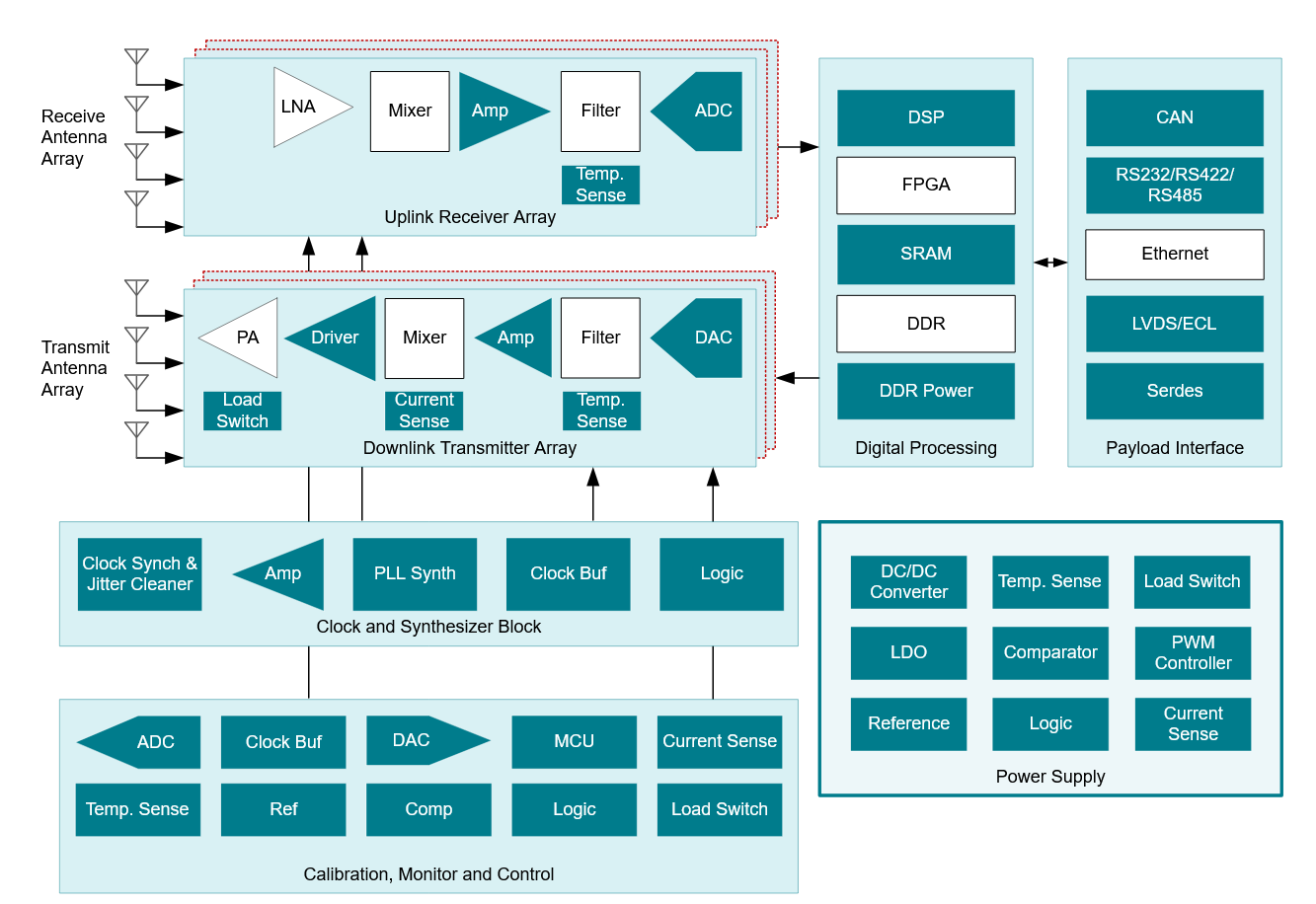

通信有效载荷-方框图

| 有奖活动 | |

|---|---|

| 硬核工程师专属补给计划——填盲盒 | |

| “我踩过的那些坑”主题活动——第002期 | |

| 【EEPW电子工程师创研计划】技术变现通道已开启~ | |

| 发原创文章 【每月瓜分千元赏金 凭实力攒钱买好礼~】 | |

| 【EEPW在线】E起听工程师的声音! | |

| 高校联络员开始招募啦!有惊喜!! | |

| 【工程师专属福利】每天30秒,积分轻松拿!EEPW宠粉打卡计划启动! | |

| 送您一块开发板,2025年“我要开发板活动”又开始了! | |