状态机的基本概念是:由状态寄存器和组合逻辑电路构成,能够根据控制信号按照预先设定的状态进行状态转移,是协调相关信号动作、完成特定操作的控制中心。

状态机分为两大类:摩尔(Moore)型状态机和米莉(Mealy)型状态机。摩尔型状态机的输出只和当前状态有关,与当前输入无关,输出会在一个完整的时钟周期内保持稳定,即使此时输入信号有变,输出也不会变化。而米莉型状态机的输出不仅和状态有关,而且和输入有关系。

在Verilog中,状态机主要用于同步时序逻辑的设计,能够在有限个状态之间按一定要求和规律切换时序电路的状态。状态的切换方向不但取决于各个输入值,还取决于当前所在状态。

状态机在硬件设计中具有重要的作用,可以大大简化分多个时间完成一个任务的工作。通过状态迁移,状态机可以完成一些特定的顺序逻辑,这在自动化控制系统、游戏开发、机场安检系统等应用场景中都有广泛的应用。

硬件设计很讲究并行设计思想,虽然用Verilog描述的电路大都是并行实现的,但是对于实际的工程应用,往往需要让硬件来实现一些具有一定顺序的工作,这就要用到状态机的思想。什么是状态机呢?简单的说,就是通过不同的状态迁移来完成一些特定的顺序逻辑。硬件的并行性决定了用 Verilog描述的硬件实现(譬如不同的always语句)都是并行执行的,那么如果希望分多个时间完成一个任务,怎么办?也许可以用多个使能信号来衔接多个不同的模块,但是这样做多少显得有些繁琐。状态机的提出就会大大简化这一工作。

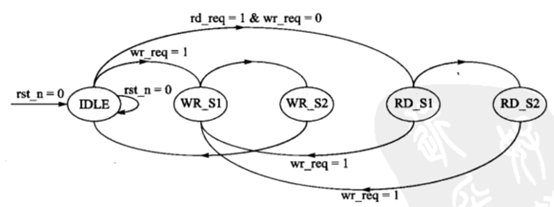

下面举一个 SRAM 控制的例子来说明状态机。如图所示,它表示了一个SRAM 控

制状态的变化。

SRAM状态机:

在Verilog中,可以使用一种基于case语句的方式来描述状态机。通过case语句配合assign语句或always块,可以清晰地定义每个状态下的行为以及状态之间的转移条件。下面是一个简单的例子:

module simple_fsm ( input wire clk, input wire reset, input wire start, output reg done);// 状态定义 parameter IDLE = 2'b00; parameter WORKING = 2'b01;parameter FINISHED = 2'b10; reg [1:0] state, next_state; // 状态机逻辑always @(posedge clk or posedge reset) begin if (reset) begin state <= IDLE; done <= 1'b0; end else begin state <= next_state; end end // 状态转移规则always @(state) begin case (state) IDLE: begin if (start) next_state = WORKING; else next_state = IDLE; end WORKING: begin next_state = FINISHED; end FINISHED: begin next_state = IDLE; done = 1'b1; end endcaseendendmodule

状态机是一种能够描述具有逻辑顺序和时序顺序的事件的方法,特别适合描述那些存在先后顺序以及其它规律性事件。在您提供的例子中,状态机根据复位信号rst_n、写请求信号wr_req和读请求信号rd_req的变化,在几个固定的状态间进行切换,如IDLE、WR_S1、RD_S1等。这样做的好处在于,每当需要操作SRAM时,其他模块只需发出相应的请求信号,系统就能自动进入相应状态并进行相应的操作。

状态机的基本要素包括输入、输出和状态。输入是引发状态变化的条件,如wr_req和rd_req的变化;输出是状态变化后引起的变化,如控制总线、地址总线和数据总线的输出值;状态则是描述系统当前所处的情况,如IDLE、WR_S1等。

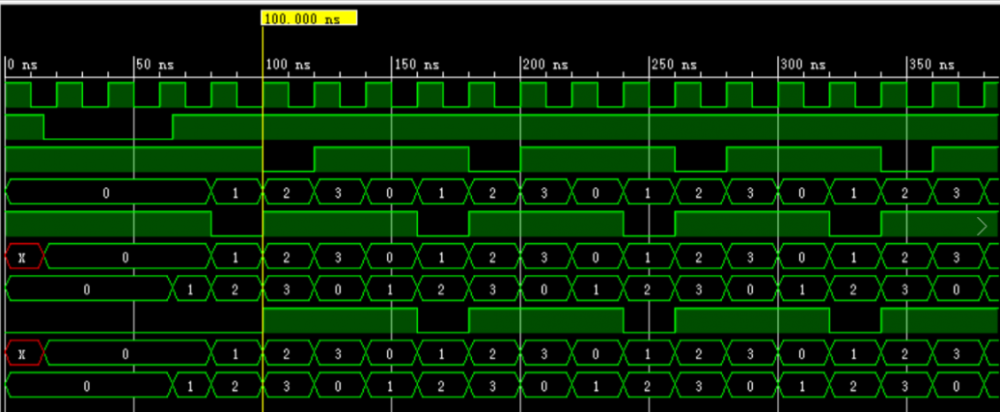

测试文件如下:

`timescale 1ns / 1ps // // Company: // Engineer: guoliang CLL // // Create Date: 2020/02/21 00:35:17 // Design Name: // Module Name: seq_gen_tsb // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // // module seq_gen_tsb( ); // port reg clk; reg rst_n; wire seq1,seq2,seq3; // clk initial begin clk = 1'b1; forever #10 clk = ~clk; end // initial begin rst_n = 1'b1; #15 rst_n = 1'b0; #50 rst_n = 1'b1; end // instantation //seq_gen_shift inst( //seq_gen_count inst( seq_gen_fsm1 inst( .clk(clk), .rst_n(rst_n), .seq(seq1) ); seq_gen_fsm2 inst2( .clk(clk), .rst_n(rst_n), .seq(seq2) ); seq_gen_fsm inst3( .clk(clk), .rst_n(rst_n), .seq(seq3) ); endmodule

输出结果:

根据状态机的特性和实现方式的不同,可以将其分为Moore型状态机和Mealy型状态机。Moore型状态机的状态变化仅和当前状态有关,而与输入条件无关;而Mealy型状态机的状态变化不仅与当前的状态有关,还取决于当前的输入条件。

在实际设计中,我们一般使用有限状态机(FSM),因为无限状态机(ISM)的状态数量是无限的,没有明确的转移条件和转移方向,这在实际应用中很难实现。有限状态机包含一组状态、一组输入符号集、一个起始状态以及一个映射输入符号和当前状态到下一状态的转换函数。当输入符号串时,模型随即进入起始状态,并根据转换函数进行状态转移。

通过状态机,我们可以将系统的各种状态和转换规则明确地定义出来,从而更容易地理解和修改代码。此外,状态机还可以提高系统的可靠性和稳定性,通过明确地定义状态转换和事件处理逻辑,可以更有效地预防和处理错误。

我要赚赏金

我要赚赏金