1. 时序设计的目标就是实现对接收端输入数据的可靠采样;

2. 时序设计需要注意的参数

时钟频率 Clk

时钟周期 Tcycle

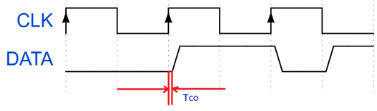

TCO

输出数据相对时钟的延迟;数据发送端受制造工艺的影响,在发出时钟后,数据出现在器件引脚上需要一定的延迟,这段延迟就是TCO;

TSU(min):接收端对输入信号建立时间的要求

TH(min):接收端对输入信号保持时间的要求

L:信号走线长度

Tflight:信号在PCB上的传输延时,外层的单位延时为140ps/inch,内层为180ps/inch,根据信号走线长度L和单位延时可计算出Tflight

TSU(margin):输入信号建立时间裕量

为实现可靠采样,TSU(margin)=TSU-TH(min)>0

TH(margin):输入信号保持时间裕量

为实现可靠采样,TH(margin)=TH-TH(min)>0

- DDR时序设计需要注意的参数

双边沿采样周期不能用Tcycle=Tck/2表示,需要从资料中提取时钟占空比参数。如占空比为45/55,频率为100MHz,那么高电平和低电平时间分别为 4.5ns 和 5.5ns ,采样周期应该取2个时间的最小值,即4.5ns。

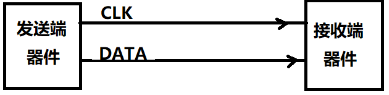

源同步系统

源同步是指时钟和数据均由发送端器件发出,在接收端,利用接收到的CLK采样数据信号DATA。a. 发送端的时序--TCO(TCO(min)、TCO(max))  b. 传输路径上的延时--Tflight-clk和Tflight-datac. 接收端的时序分析

b. 传输路径上的延时--Tflight-clk和Tflight-datac. 接收端的时序分析

分享一个时序的案例:①发送端数据线上发出信号DATA1,驱动时钟为CLK1;②数据线和时钟等长Tflight-data = Tflight-clk;分析:那么由于TCO的存在,CLK1不能作为接收端DATA1的时钟参考沿;如何修改:①Tflight-data > Tflight-clk,参考下一个时钟CLK2;②Tflight-data < Tflight-clk,依旧参考CLK1;