PCBlayout信号线之间做包地处理

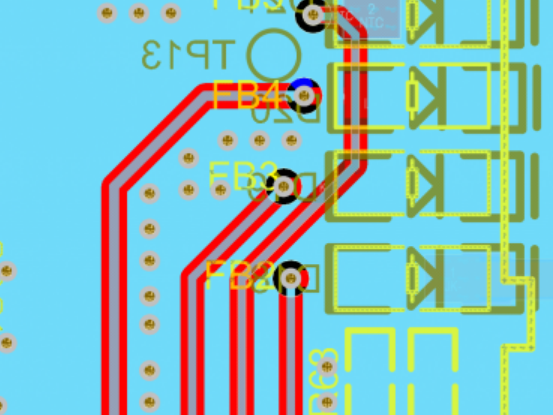

PCBlayout中会遇到单总线,串口线TX、RX,IIC的时钟、数据线并排走的情况,为了防止互相干扰。有没有之间间隔拉宽一点,并且灌入铜皮,做所谓的包地处理。这个是有必要的吗?之前的工作经验,有看到一个老工程师都是这么处理的,比如串口走线到蓝牙的TX、RX之间。请问信号之间做包地处理它防止互相干扰的机理是什么?

| 有奖活动 | |

|---|---|

| 硬核工程师专属补给计划——填盲盒 | |

| “我踩过的那些坑”主题活动——第002期 | |

| 【EEPW电子工程师创研计划】技术变现通道已开启~ | |

| 发原创文章 【每月瓜分千元赏金 凭实力攒钱买好礼~】 | |

| 【EEPW在线】E起听工程师的声音! | |

| 高校联络员开始招募啦!有惊喜!! | |

| 【工程师专属福利】每天30秒,积分轻松拿!EEPW宠粉打卡计划启动! | |

| 送您一块开发板,2025年“我要开发板活动”又开始了! | |