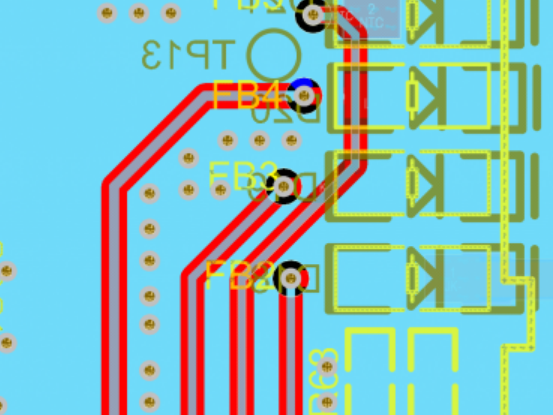

PCBlayout信号线之间做包地处理

PCBlayout中会遇到单总线,串口线TX、RX,IIC的时钟、数据线并排走的情况,为了防止互相干扰。有没有之间间隔拉宽一点,并且灌入铜皮,做所谓的包地处理。这个是有必要的吗?之前的工作经验,有看到一个老工程师都是这么处理的,比如串口走线到蓝牙的TX、RX之间。请问信号之间做包地处理它防止互相干扰的机理是什么?

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |

| 【S32K3XX】LIN 通讯模块使用被打赏¥31元 | |

| 【FreeRtos】FreeRtos + MPU模块的配置使用被打赏¥32元 | |