有时候,为了CE/RE好过,就在输出端放置一级共模电感。

但是,做工业平板电源/导轨电源,要求电源抗扰等级较高,RS/CS/EFT/输出EFT等等测试强度高。

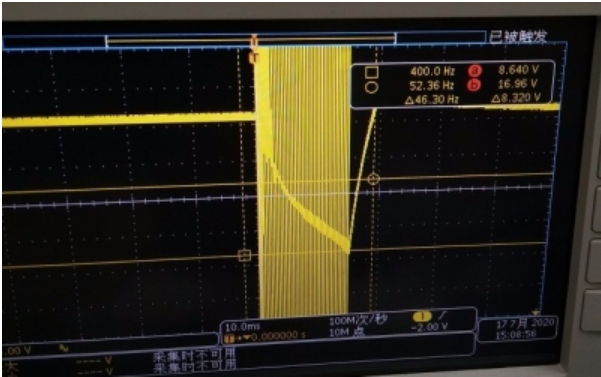

会发现,如果不把输出那个共模电感短路掉,在做如上抗扰测试时,输出的电压会掉坑超过规格范围。

哪位大神知道,共模以什么模型或者形式干扰了输出电压环(光耦或431回路)?

小弟,实际整改发现,把431回路面积减小有好处。把输出功率整流环路面积减小也有好处,共模之后靠近输出端放置对大地的Y电容也有好处,只是不知道这个共模是怎么产生影响的?

| 有奖活动 | |

|---|---|

| 硬核工程师专属补给计划——填盲盒 | |

| “我踩过的那些坑”主题活动——第002期 | |

| 【EEPW电子工程师创研计划】技术变现通道已开启~ | |

| 发原创文章 【每月瓜分千元赏金 凭实力攒钱买好礼~】 | |

| 【EEPW在线】E起听工程师的声音! | |

| 高校联络员开始招募啦!有惊喜!! | |

| 【工程师专属福利】每天30秒,积分轻松拿!EEPW宠粉打卡计划启动! | |

| 送您一块开发板,2025年“我要开发板活动”又开始了! | |

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| Chaos-nano:专为低资源单片机设计的轻量级协作式异步操作系统(ATMEGA328P轻量级操作系统)—— 详细介绍被打赏¥16元 | |

| FPGA配置被打赏¥10元 | |

| Chaos-nano协作式异步操作系统:赋能MicrochipAVR8位单片机的革新之路被打赏¥15元 | |

| 基于esp32开发时串口工具的注意点被打赏¥24元 | |

| 基于FireBeetle2ESP32-C5开发板的舵机控制被打赏¥20元 | |

| 【分享开发笔记,赚取电动螺丝刀】MAX78000开发板制作的电子相册被打赏¥32元 | |

| 基于FireBeetle2ESP32-C5开发板的超声波测距及显示被打赏¥21元 | |

| FireBeetle2ESP32-C5上RTC电子时钟的实现被打赏¥25元 | |

| 【分享开发笔记,赚取电动螺丝刀】MAX78000开发板读取SD卡被打赏¥23元 | |

| 【S32K3XX】Standby RAM 重启后数据异常问题调查被打赏¥38元 | |