有时候,为了CE/RE好过,就在输出端放置一级共模电感。

但是,做工业平板电源/导轨电源,要求电源抗扰等级较高,RS/CS/EFT/输出EFT等等测试强度高。

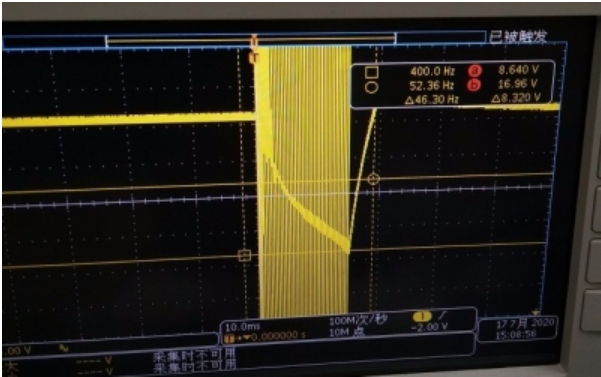

会发现,如果不把输出那个共模电感短路掉,在做如上抗扰测试时,输出的电压会掉坑超过规格范围。

哪位大神知道,共模以什么模型或者形式干扰了输出电压环(光耦或431回路)?

小弟,实际整改发现,把431回路面积减小有好处。把输出功率整流环路面积减小也有好处,共模之后靠近输出端放置对大地的Y电容也有好处,只是不知道这个共模是怎么产生影响的?

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |

| 【S32K3XX】LIN 通讯模块使用被打赏¥31元 | |

| 【FreeRtos】FreeRtos + MPU模块的配置使用被打赏¥32元 | |