一、场效应管的介绍

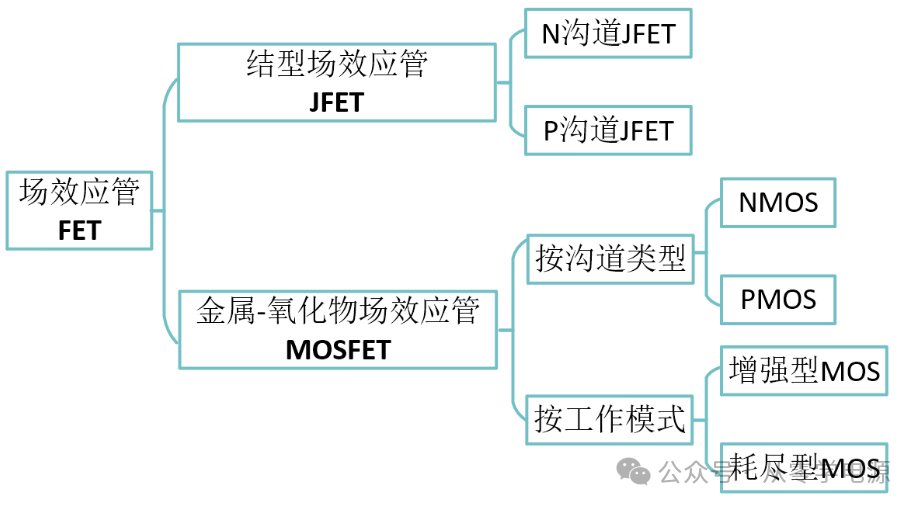

MOSFET(Metal Oxide Semiconductor Field Effect Transistor 全称:金属-氧化物-半导体场效应晶体管),简称MOS管,属于场效应管(FET)的一种。

场效应管利用控制输入回路的电场效应来控制输出回路电流的一种半导体器件。其中最常用的是增强型NMOS。

为什么是NMOS?——NMOS具有更快的速度,更小的面积,更简单的工艺。因为NMOS的载流子是电子,PMOS的载流子是空穴,电子的迁移率是空穴的2-3倍,在相同电场作用下,电子跑得比空穴快。相同尺寸大小的NMOS和PMOS相比,NMOS导通电流可以做到更大。

为什么是增强型?——增强型在不加栅源电压时没有沟道,器件默认是关闭的。耗尽型在没有栅源电压时就存在沟道,器件默认是导通的,需要加负压才能关闭。由于耗尽型默认开启,不符合数字逻辑思维,不符合低功耗设计,且制造工艺复杂,故耗尽型很少见。

为什么是MOS?——MOSFET符合现代数字芯片CMOS工艺,JFET与标准CMOS工艺不兼容,不易高密度集成,且JFET通常为耗尽型,不符合低功耗理念。JFET只适用于对噪声、可靠性要求高的特殊模拟应用。

二、MOSFET的原理

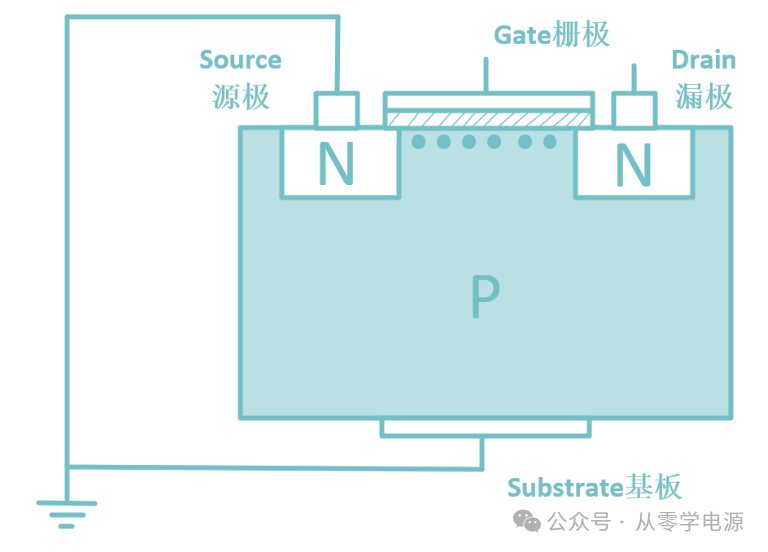

以增强型NMOS管为例,栅极与衬底之间存在很薄的绝缘层(SiO2),将栅极金属和P型衬底隔开。

为什么源极和衬底短接在一起?衬底与源极短接,电位相同,可以让该PN结处于零偏置状态,防止其正向导通影响MOS管工作,同时也能避免衬底偏置效应影响Vth阈值电压。

在衬底P型半导体里,由于存在少量的自由电子,故当Vgs存在电压时,衬底中的少量电子受电场作用向栅极靠近并聚集,形成N型沟道,连通源极和漏极。在源漏极加上电压时,电子就可以通过沟道从源极流向漏极,形成漏极电流Id。

其中绝缘层越薄,电场作用越明显,形成导通沟道的阈值电压越小。但是电路设计者(DE)无法改变阈值电压(Vth),阈值电压由工艺决定,设计者只能基于晶圆厂提供的PDK进行设计,PDK中的器件模型参数是固定的。

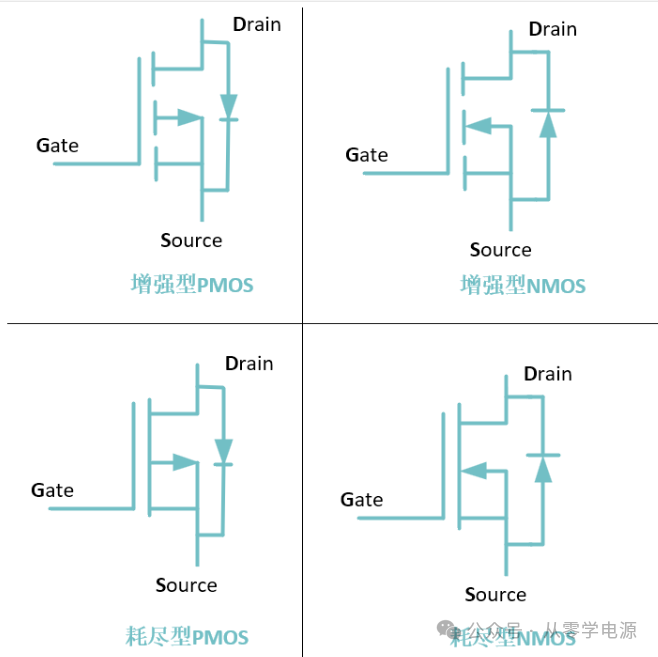

如何从符号上区分增强型和耗尽型?由于增强型MOS的沟道在Vgs=0时还未形成,所以符号上沟道是断开的,而耗尽型MOS的沟道在没有Vgs时已经形成,所以在符号上沟道是连续的。

如何从符号上区分PMOS、NMOS?由于PMOS和NMOS的沟道类型不同,沟道处的箭头方向都是从P指向N,所以可以通过观察箭头方向来确定沟道类型。箭头指向外,则沟道为P型;箭头指向沟道处,则沟道为N型。

如何确定体二极管方向?以NMOS为例,由于源极S与衬底相连,且衬底(P型)与漏极(N型)可以看作一个二极管,又被称为体二极管(body diode),故存在源极-漏极之间的二极管,二极管导通方向由源极指向漏极,从符号上看二极管方向与沟道处的箭头方向相同。

如何区分源极、漏极、栅极?MOS管脚中栅极(Gate)与其他极绝缘,而源极(Source)与衬底(Substrate)相连,故连接到符号中间衬底沟道的都是源极,不连接的是漏极。

三、MOSFET的特性

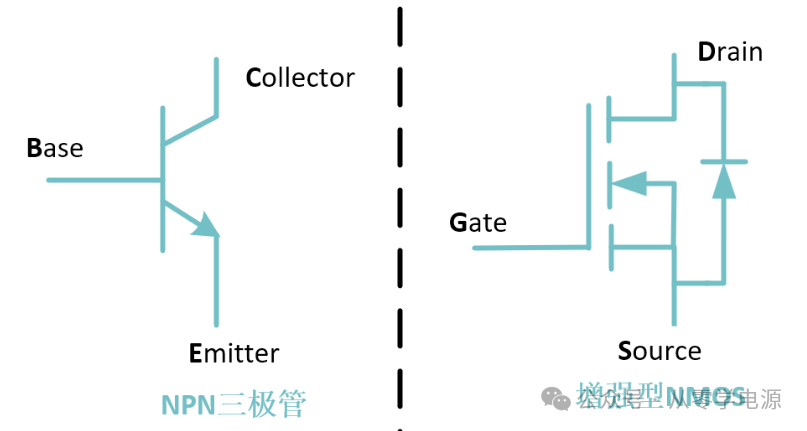

以NPN三极管BJT为例,对比介绍增强型NMOS的特性

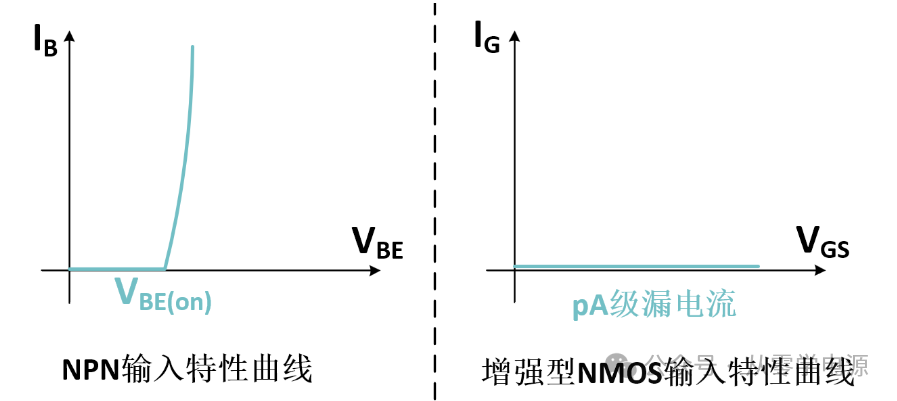

3.1 输入特性曲线

三极管BJT的输入特性曲线是VBE与IB之间的关系曲线,类似于二极管的正向特性曲线。

MOS管的输入特性曲线是VGS与IG之间的关系曲线,由于G极下方具有绝缘层,栅极与沟道之间构成一个电容,直流状态下IG只有微小的漏电流。

由于MOS管的栅极绝缘,输入阻抗极高,不吸取电流,故通常不讨论MOS管的输入特性曲线。

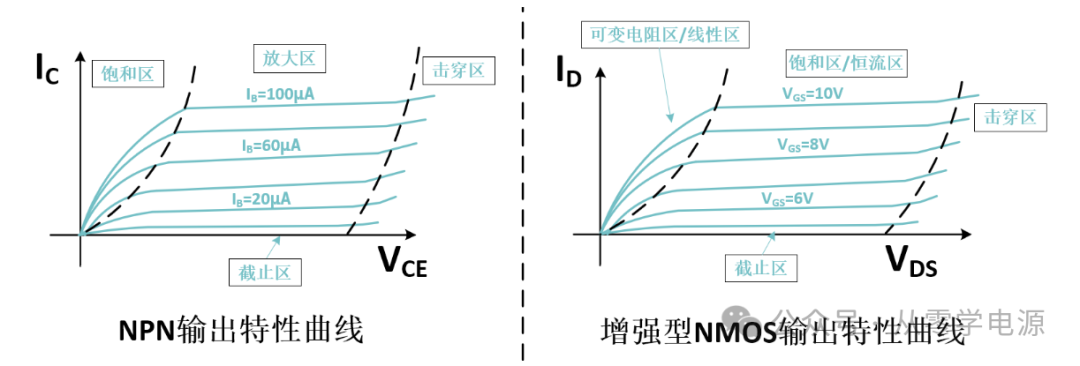

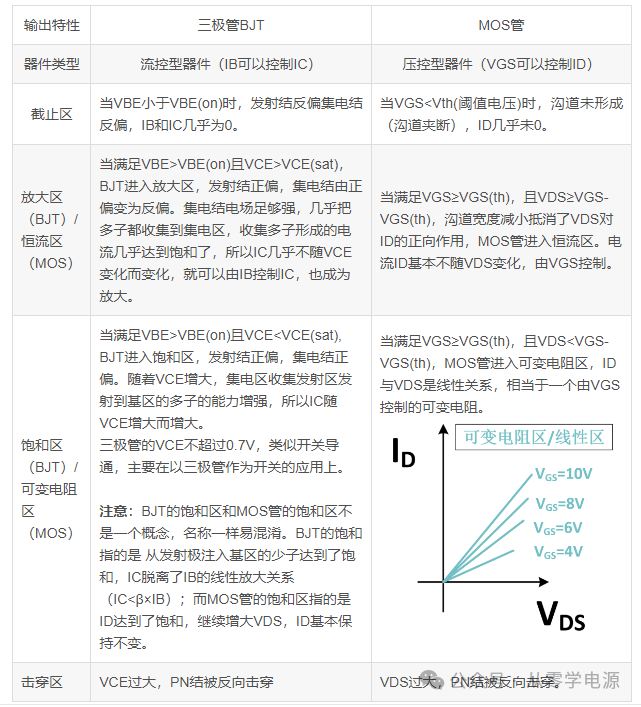

3.2 输出特性曲线

三极管以共发射极配置,输出特性曲线是VCE与IC之间的关系曲线,参变量以基极电流IB作为不同的曲线参数。

MOS管的输出特性曲线是VDS与ID之间的关系曲线,参变量以栅源电压VGS作为不同的曲线参数。

MOS管的恒流区/饱和区,相当于三极管的放大区:

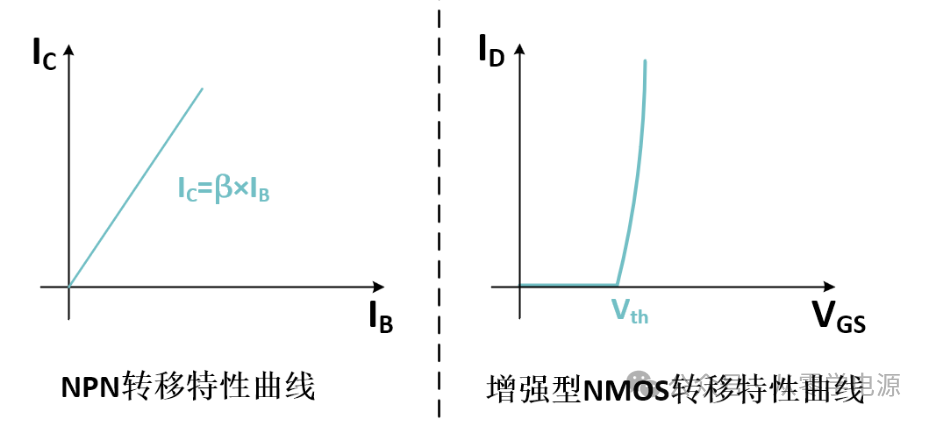

3.3 转移特性曲线

转移特性曲线反映的是输入量对输出量的控制能力,三极管的转移特性曲线是IB与IC之间的关系曲线,MOS管的转移特性曲线是VGS与ID之间的关系曲线。

BJT是电流控型器件,IB控制IC,IC与IB呈线性关系;MOS管是压控型器件,VGS控制ID,是平方律的关系。

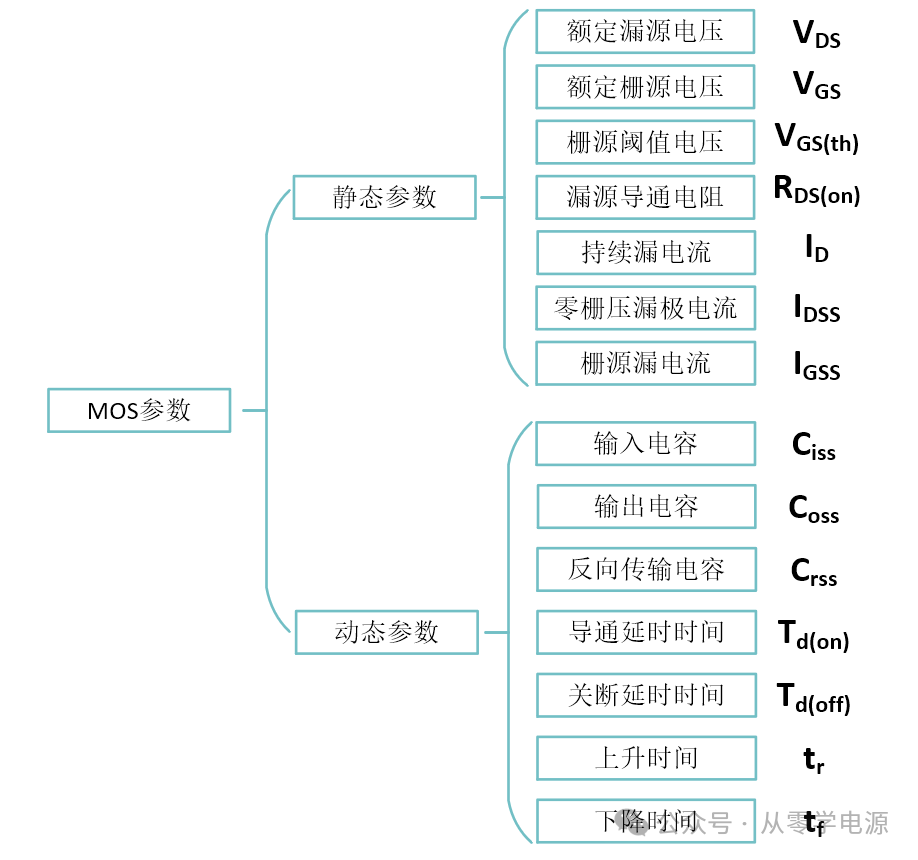

四、MOSFET的参数

针对电源应用,需要考虑的MOS管重要参数包含以下:

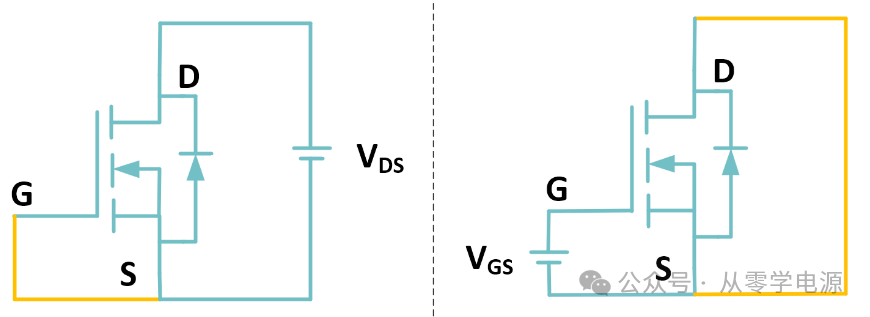

4.1 额定漏源电压VDS、额定栅源电压VGS

额定漏源电压VDS:栅极G和源极S短路,在漏极D和源极S所能施加的最大电压值,表明了MOS管在关断状态下,漏源极之间能承受的最大电压,可理解为源漏击穿电压,具有正温度系数,高温下,MOS管能承受的瞬时电压反而比室温下更高,而低温下实际击穿电压会低于标称值,选型时仍需要留有充分裕量,避免尖峰电压和瞬态冲击损坏MOS。

额定栅源电压VGS:漏极D和源极S短路,在漏极G和源极S所能施加的最大电压值。如果超过该额定电压,可能导致栅氧化层损伤。

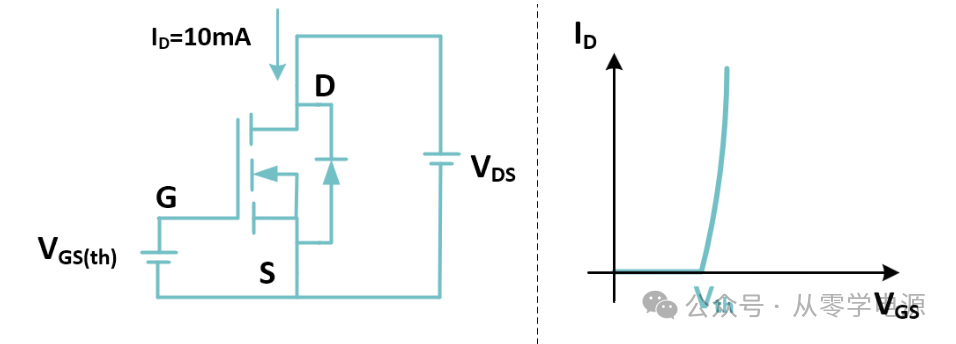

4.2 栅源阈值电压VGS(th)

阈值电压VGS(th):在MOS的栅源之间加的可以形成导通沟道的最小电压。VGS达到阈值电压后,MOS从截止状态转变为导通状态。阈值电压具有负温度系数,高温下避免噪声超过阈值电压发生误动作。一般来说,高阈值电压的MOS具有较小的栅源漏电流,但是其开关速度较慢,动态功耗较大。

4.3 漏源导通电阻RDS(on)

漏源导通电阻RDS(on):MOS管处于导通状态时,源漏之间的等效电阻,具有正温度特性。

尤其在大电流应用中,较低的导通电阻可以降低MOS的导通损耗,减少MOS发热,提升电源的转化效率。通常RDS(on)与器件尺寸、成本成反比。高压器件RDS(on)一般高于低压器件。设计中需要综合考虑成本、体积和效率。

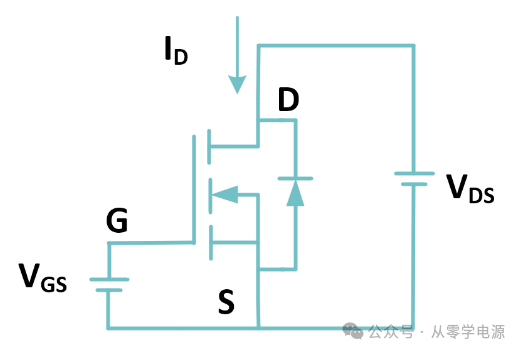

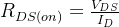

4.4 持续漏电流 ID,零栅压漏极电流IDSS,栅源漏电流IGSS

ID,零栅压漏极电流IDSS,栅源漏电流IGSS

持续漏电流ID表明MOS管支持工作的最大直流电流,受温度、导通阻抗、封装等影响。

零栅压漏极电流IDSS表明MOS管在栅源短路状态下(VGS=0),漏极与源极之间加额定电压下的泄漏电流。该值具有正温度系数。

栅源漏电流IGSS表明MOS管在源漏短路状态下(VDS=0),栅极与源极之间加额定电压下的泄露电流。

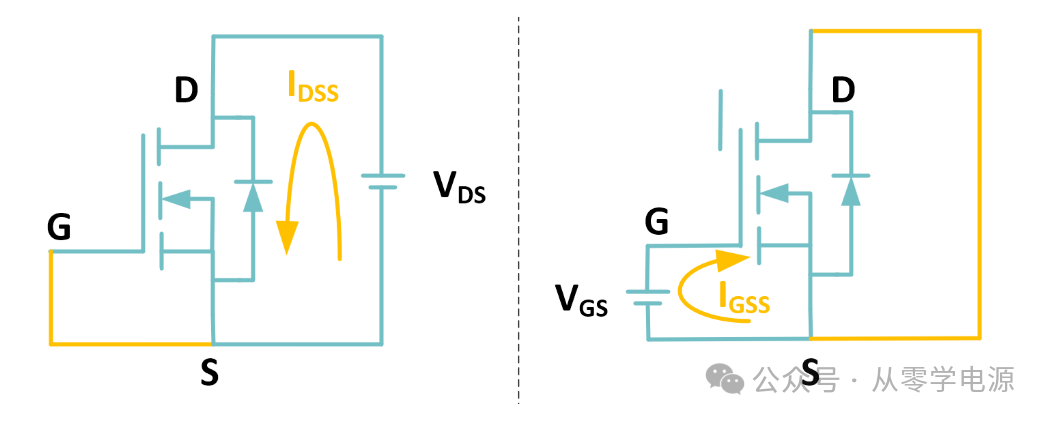

4.5 输入电容Ciss、输出电容Coss、反向传输电容Crss

输入电容(Ciss)表明漏源短接下,交流信号测得的栅极和源极之间的电容,其代表着驱动MOS管时栅极驱动电路需要充电的总电容,直接影响MOS管的栅极电荷Qg和驱动电流。Ciss越大,开关MOS所需要的能量和时间就越大。

Ciss=Cgs+Cgd

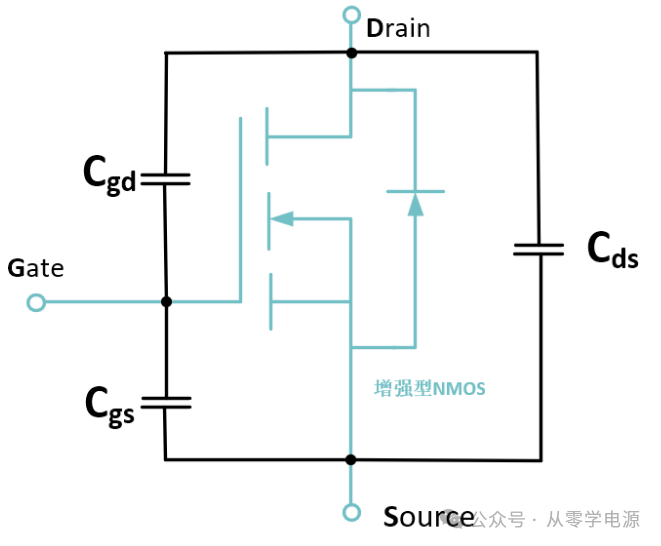

输出电容(Coss)表明栅源短接下,交流信号测得的漏极与源极之间的电容,其代表着MOS管在关断时,漏极和源极之间存在的总电容。

Coss=Cds+Cgd

在硬开关电路中,MOS管由导通到关断时,其VDS会从0上升到母线电压,这个电压会对Coss充电,消耗的能量称为关断损耗。

在软开关电路中,例如LLC,输出电容Coss是谐振电容的一部分,其大小直接影响谐振频率。

对于桥式电路,若Coss过大,由于另一管开关引起的快速电压变化(dV/dt)通过Coss充放电电流,误触发关断的MOS管使其导通。

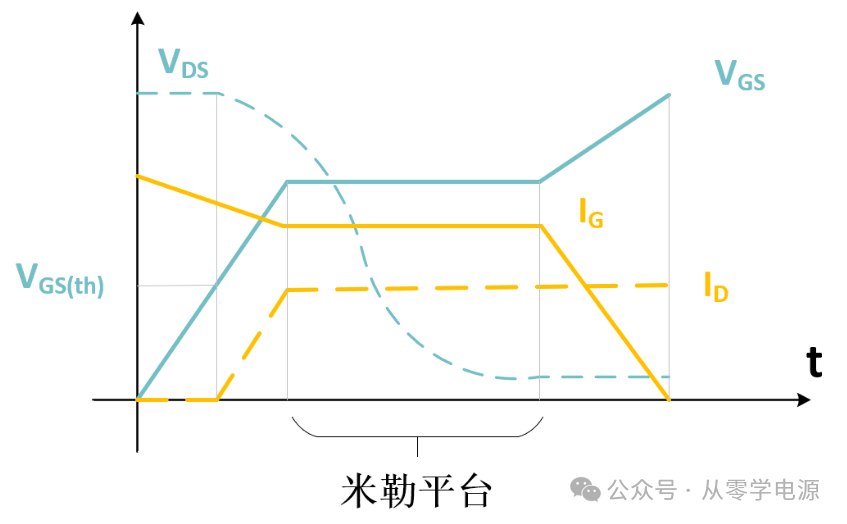

反向传输电容(Crss)表明源极接地,测漏极和栅极之间的电容。由于其会引发米勒效应,故也称作米勒电容。米勒效应会阻止Vgs上升,从而也就阻止了Vds的下降。米勒电容会显著延长开关过程的平台阶段,其是造成开关损耗(尤其是开通损耗:ID×VDS)的主要原因,影响开关上升、下降时间和关断延时时间。

Crss=Cgd

输入电容(Ciss)、输出电容(Coss)、反向传输电容(Crss)共同决定了MOS管的交流特性,影响MOS管的开关速度、损耗、电路稳定性。

4.6 导通、关断延时时间Td(on)/Td(off)、上升、下降时间TrTf

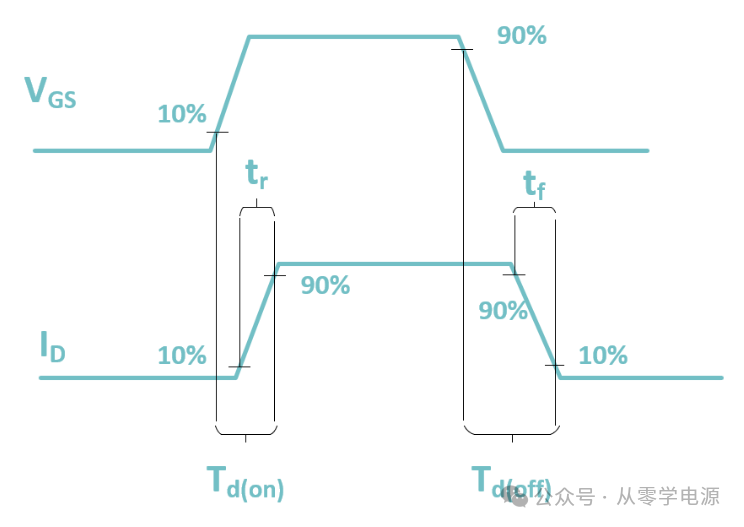

Td(on)导通延时时间:从栅极驱动电压VGS上升到其幅值的10%开始,到漏极电流上升到其幅值的90%的时间间隔。

Td(off)关断延时时间:从栅极驱动电压 VGS下降到其幅值的90%开始,到漏极电流下降到其幅值的90%的时间间隔。

tr上升时间:漏极电流从其幅值的10%上升到90%所需的时间。

tf下降时间:漏极电流从其幅值的90%下降到10%所需的时间。

如何优化缩短这些时间呢?

选择本身开关速度快(Qg低栅极电压和低寄生电容)的MOSFET

提高栅极驱动能力(增加驱动电压、减小驱动电阻)

使用专用的栅极驱动IC,可提供瞬间的峰值电流

4.7 安全动作区SOA

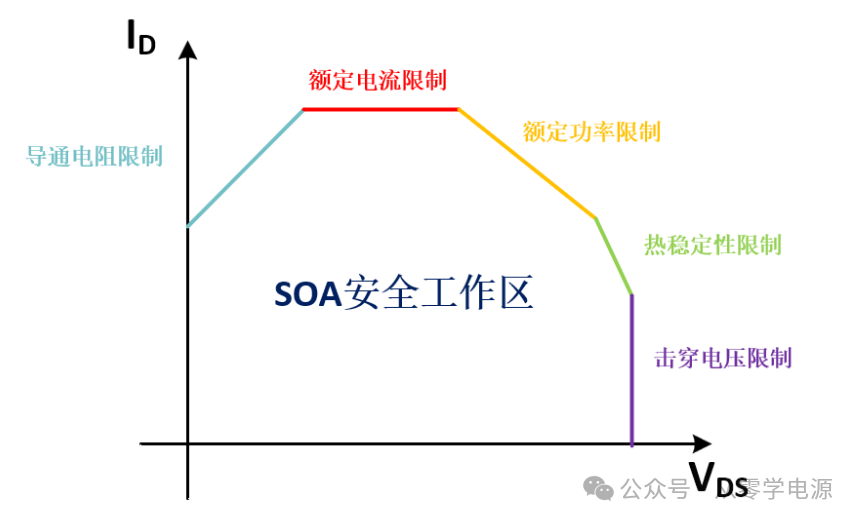

MOS管的SOA(Safe Operating Area)结合了MOS的多种物理限制,只要MOS的工作点落在这个区域,器件就不会因过应力而损坏,超过SOA边界可能导致MOS永久性失效。

我要赚赏金

我要赚赏金