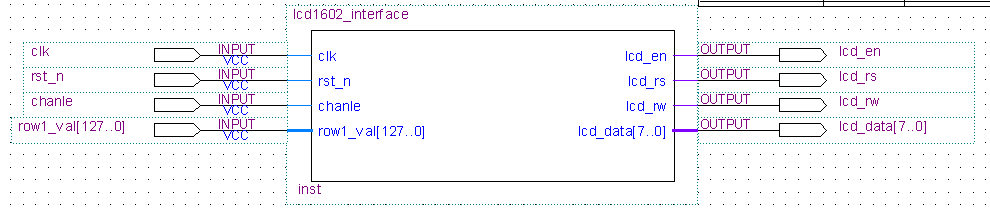

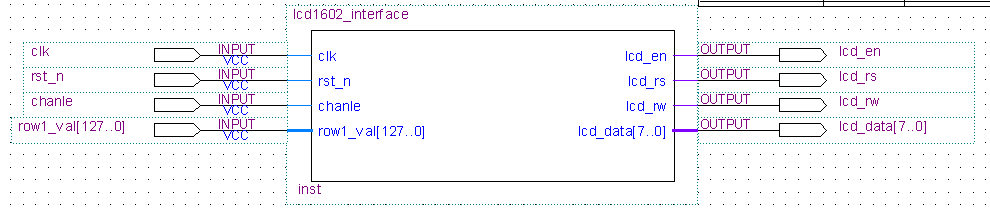

21、模块例化三:LCD1602模块——12.11.30

row1_val[127..0]:数据输入,16个字符;

chanle:0-第一行;1-第二行;

注意:这个模块值时候调用,不能单独建立工程,FPGA没那么多3.3V的IO口啊

verilog程序:

module lcd1602_interface

(

input clk,

input rst_n,

input chanle,

input[127:0] row1_val,

output lcd_en, // lcd enable

output reg lcd_rs, // record,statement

output lcd_rw,

output reg[7:0] lcd_data

);

// reg [127:0] row1_val="Hello!I'm Anmko.";

assign lcd_rw = 1'b0;

reg [15:0] cnt;

always @ (posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt <= 0;

else

cnt <= cnt + 1'b1;

end

assign lcd_en = cnt[15]; //lcd enable,keep same time; >1000ns

parameter IDLE = 8'h00;

// Initialization. write instructions

parameter DISP_SET = 8'h01; // entry mode set

parameter DISP_OFF = 8'h03; // display off

parameter CLR_SCR = 8'h02; // clean display

parameter CURSOR_SET1 = 8'h06; // display shift set

parameter CURSOR_SET2 = 8'h07; // display on and cursor set

// display the 1st row

parameter ROW1_ADDR = 8'h05; // write the start address of the 1st row

parameter ROW1_0 = 8'h04;

parameter ROW1_1 = 8'h0C;

parameter ROW1_2 = 8'h0D;

parameter ROW1_3 = 8'h0F;

parameter ROW1_4 = 8'h0E;

parameter ROW1_5 = 8'h0A;

parameter ROW1_6 = 8'h0B;

parameter ROW1_7 = 8'h09;

parameter ROW1_8 = 8'h08;

parameter ROW1_9 = 8'h18;

parameter ROW1_A = 8'h19;

parameter ROW1_B = 8'h1B;

parameter ROW1_C = 8'h1A;

parameter ROW1_D = 8'h1E;

parameter ROW1_E = 8'h1F;

parameter ROW1_F = 8'h1D;

// display the 2nd row

parameter ROW2_ADDR = 8'h1C; // write the start address of the 2nd row

parameter ROW2_0 = 8'h14;

parameter ROW2_1 = 8'h15;

parameter ROW2_2 = 8'h17;

parameter ROW2_3 = 8'h16;

parameter ROW2_4 = 8'h12;

parameter ROW2_5 = 8'h13;

parameter ROW2_6 = 8'h11;

parameter ROW2_7 = 8'h10;

parameter ROW2_8 = 8'h30;

parameter ROW2_9 = 8'h31;

parameter ROW2_A = 8'h33;

parameter ROW2_B = 8'h32;

parameter ROW2_C = 8'h36;

parameter ROW2_D = 8'h37;

parameter ROW2_E = 8'h35;

parameter ROW2_F = 8'h34;

reg [5:0] current_state, next_state; // current state, next state

// FSM: always1

always @ (posedge lcd_en or negedge rst_n) begin

if(!rst_n) current_state <= IDLE;

else current_state <= next_state;

end

// FSM: always2

always begin

case(current_state)

IDLE : next_state = DISP_SET;

// Initialization. write instructions

DISP_SET : next_state = DISP_OFF;

DISP_OFF : next_state = CLR_SCR;

CLR_SCR : next_state = CURSOR_SET1;

CURSOR_SET1 : next_state = CURSOR_SET2;

CURSOR_SET2 : begin

if(!chanle)

next_state = ROW1_ADDR;

else

next_state = ROW2_ADDR;

end

// display the 1st row

ROW1_ADDR : next_state = ROW1_0;

ROW1_0 : next_state = ROW1_1;

ROW1_1 : next_state = ROW1_2;

ROW1_2 : next_state = ROW1_3;

ROW1_3 : next_state = ROW1_4;

ROW1_4 : next_state = ROW1_5;

ROW1_5 : next_state = ROW1_6;

ROW1_6 : next_state = ROW1_7;

ROW1_7 : next_state = ROW1_8;

ROW1_8 : next_state = ROW1_9;

ROW1_9 : next_state = ROW1_A;

ROW1_A : next_state = ROW1_B;

ROW1_B : next_state = ROW1_C;

ROW1_C : next_state = ROW1_D;

ROW1_D : next_state = ROW1_E;

ROW1_E : next_state = ROW1_F;

ROW1_F : begin

if(!chanle)

next_state = ROW1_ADDR;

else

next_state = ROW2_ADDR;

end

// display the 2nd row

ROW2_ADDR : next_state = ROW2_0;

ROW2_0 : next_state = ROW2_1;

ROW2_1 : next_state = ROW2_2;

ROW2_2 : next_state = ROW2_3;

ROW2_3 : next_state = ROW2_4;

ROW2_4 : next_state = ROW2_5;

ROW2_5 : next_state = ROW2_6;

ROW2_6 : next_state = ROW2_7;

ROW2_7 : next_state = ROW2_8;

ROW2_8 : next_state = ROW2_9;

ROW2_9 : next_state = ROW2_A;

ROW2_A : next_state = ROW2_B;

ROW2_B : next_state = ROW2_C;

ROW2_C : next_state = ROW2_D;

ROW2_D : next_state = ROW2_E;

ROW2_E : next_state = ROW2_F;

ROW2_F : begin

if(!chanle)

next_state = ROW1_ADDR;

else

next_state = ROW2_ADDR;

end

default : next_state = IDLE ;

endcase

end

// FSM: always3

always @ (posedge lcd_en or negedge rst_n) begin

if(!rst_n)

begin

lcd_rs <= 0;

lcd_data <= 8'hxx;

end

else

begin

// write lcd_rs

case(next_state)

IDLE : lcd_rs <= 0;

// Initialization. write instructions

DISP_SET : lcd_rs <= 0;

DISP_OFF : lcd_rs <= 0;

CLR_SCR : lcd_rs <= 0;

CURSOR_SET1 : lcd_rs <= 0;

CURSOR_SET2 : lcd_rs <= 0;

// write data and display the 1st row

ROW1_ADDR : lcd_rs <= 0;

ROW1_0 : lcd_rs <= 1;

ROW1_1 : lcd_rs <= 1;

ROW1_2 : lcd_rs <= 1;

ROW1_3 : lcd_rs <= 1;

ROW1_4 : lcd_rs <= 1;

ROW1_5 : lcd_rs <= 1;

ROW1_6 : lcd_rs <= 1;

ROW1_7 : lcd_rs <= 1;

ROW1_8 : lcd_rs <= 1;

ROW1_9 : lcd_rs <= 1;

ROW1_A : lcd_rs <= 1;

ROW1_B : lcd_rs <= 1;

ROW1_C : lcd_rs <= 1;

ROW1_D : lcd_rs <= 1;

ROW1_E : lcd_rs <= 1;

ROW1_F : lcd_rs <= 1;

// write data, and display the 2nd row

ROW2_ADDR : lcd_rs <= 0;

ROW2_0 : lcd_rs <= 1;

ROW2_1 : lcd_rs <= 1;

ROW2_2 : lcd_rs <= 1;

ROW2_3 : lcd_rs <= 1;

ROW2_4 : lcd_rs <= 1;

ROW2_5 : lcd_rs <= 1;

ROW2_6 : lcd_rs <= 1;

ROW2_7 : lcd_rs <= 1;

ROW2_8 : lcd_rs <= 1;

ROW2_9 : lcd_rs <= 1;

ROW2_A : lcd_rs <= 1;

ROW2_B : lcd_rs <= 1;

ROW2_C : lcd_rs <= 1;

ROW2_D : lcd_rs <= 1;

ROW2_E : lcd_rs <= 1;

ROW2_F : lcd_rs <= 1;

endcase

// write lcd_data

case(next_state)

IDLE : lcd_data <= 8'hxx;

// Initialization. write instructions

DISP_SET : lcd_data <= 8'h38;

DISP_OFF : lcd_data <= 8'h08;

CLR_SCR : lcd_data <= 8'h01;

CURSOR_SET1 : lcd_data <= 8'h06;

CURSOR_SET2 : lcd_data <= 8'h0C;

// write date, and display the 1st row

ROW1_ADDR : lcd_data <= 8'h80;

ROW1_0 : lcd_data <= row1_val[127:120];

ROW1_1 : lcd_data <= row1_val[119:112];

ROW1_2 : lcd_data <= row1_val[111:104];

ROW1_3 : lcd_data <= row1_val[103: 96];

ROW1_4 : lcd_data <= row1_val[ 95: 88];

ROW1_5 : lcd_data <= row1_val[ 87: 80];

ROW1_6 : lcd_data <= row1_val[ 79: 72];

ROW1_7 : lcd_data <= row1_val[ 71: 64];

ROW1_8 : lcd_data <= row1_val[ 63: 56];

ROW1_9 : lcd_data <= row1_val[ 55: 48];

ROW1_A : lcd_data <= row1_val[ 47: 40];

ROW1_B : lcd_data <= row1_val[ 39: 32];

ROW1_C : lcd_data <= row1_val[ 31: 24];

ROW1_D : lcd_data <= row1_val[ 23: 16];

ROW1_E : lcd_data <= row1_val[ 15: 8];

ROW1_F : lcd_data <= row1_val[ 7: 0];

// write date, and display the 2nd row

ROW2_ADDR : lcd_data <= 8'hC0;

ROW2_0 : lcd_data <= row1_val[127:120];

ROW2_1 : lcd_data <= row1_val[119:112];

ROW2_2 : lcd_data <= row1_val[111:104];

ROW2_3 : lcd_data <= row1_val[103: 96];

ROW2_4 : lcd_data <= row1_val[ 95: 88];

ROW2_5 : lcd_data <= row1_val[ 87: 80];

ROW2_6 : lcd_data <= row1_val[ 79: 72];

ROW2_7 : lcd_data <= row1_val[ 71: 64];

ROW2_8 : lcd_data <= row1_val[ 63: 56];

ROW2_9 : lcd_data <= row1_val[ 55: 48];

ROW2_A : lcd_data <= row1_val[ 47: 40];

ROW2_B : lcd_data <= row1_val[ 39: 32];

ROW2_C : lcd_data <= row1_val[ 31: 24];

ROW2_D : lcd_data <= row1_val[ 23: 16];

ROW2_E : lcd_data <= row1_val[ 15: 8];

ROW2_F : lcd_data <= row1_val[ 7: 0];

endcase

end

end

endmodule

我要赚赏金

我要赚赏金