进程17、LCD数字时钟

将1602LCD组合到DS1302数字时钟模块中,实现LCD数字时钟+LED数字时钟。

顶层模块:

module DS1302(

CLK, RSTn,

SEG, DIG,

RST,

SCLK,

SIO,

SEC_Data,

MIN_Data,

HOU_Data,

LED,

YELLOW,

lcd_rs,

lcd_rw,

lcd_en,

lcd_data,

);

input CLK;

input RSTn;

input [7:0]KEY;

output [7:0]SEG;

output [7:0]DIG;

output RST;

output SCLK;

inout SIO;

output [7:0]SEC_Data;

output [7:0]MIN_Data;

output [7:0]HOU_Data;

output [7:0]LED;

output [2:0]YELLOW;

wire [3:0]Data7;

wire [3:0]Data6;

wire [3:0]Data5;

wire [3:0]Data4;

wire [3:0]Data3;

wire [3:0]Data2;

wire [3:0]Data1;

wire [3:0]Data0;

//------------------------------------------------------------

output lcd_rs ;

output lcd_rw ;

output lcd_en ;

output [7:0] lcd_data ;

wire lcd_rs;

wire lcd_rw;

wire lcd_en;

wire [7:0]lcd_data;

lcd1602_module U5

(

.CLK(CLK ),

.RSTn(RSTn ),

.lcd_rs(lcd_rs),

.lcd_rw (lcd_rw),

.lcd_en(lcd_en),

.lcd_data(lcd_data),

.Data7 ( Data7 ),

.Data6 ( Data6 ),

.Data5 ( Data5 ),

.Data4 ( Data4 ),

.Data3 ( Data3 ),

.Data2 ( Data2 ),

.Data1 ( Data1 ),

.Data0 ( Data0 )

);

endmodule

LCD1602模块

module lcd1602_module(CLK ,

RSTn ,

lcd_rs ,

lcd_rw ,

lcd_en ,

lcd_data,

Data7,Data6,Data5,Data4,Data3,Data2,Data1,Data0

);

//输入输出信号定义

input CLK ;//系统时钟输入

input RSTn ;//系统复位信号,低电平有效

output lcd_rs ;//lcd的寄存器选择输出信号

output lcd_rw ;//lcd的读、写操作选择输出信号

output lcd_en ;//lcd使能信号

output [7:0] lcd_data ;//lcd的数据总线(不进行读操作,故为输出)

input [3:0] Data7;

input [3:0] Data6;

input [3:0] Data5;

input [3:0] Data4;

input [3:0] Data3;

input [3:0] Data2;

input [3:0] Data1;

input [3:0] Data0;

//寄存器定义

reg lcd_rs ;

reg clk_div ;

reg [17:0] delay_cnt ;

reg [7:0] lcd_data ;

reg [4:0] char_cnt ;

reg [7:0] data_disp ;

reg [9:0] state ;

parameter idle = 10'b000000000,

clear = 10'b000000001,

set_function = 10'b000000010,

switch_mode = 10'b000000100,

set_mode = 10'b000001000,

shift = 10'b000010000,

set_ddram1 = 10'b000100000,

set_ddram2 = 10'b001000000,

write_ram1 = 10'b010000000,

write_ram2 = 10'b100000000;

assign lcd_rw = 1'b0;

assign lcd_en = clk_div;

always@(posedge CLK or negedge RSTn)

begin

if(!RSTn)

begin

delay_cnt<=18'd0;

clk_div<=1'b0;

end

else if(delay_cnt==18'd249999)

begin

delay_cnt<=18'd0;

clk_div<=~clk_div;

end

else

begin

delay_cnt<=delay_cnt+1'b1;

clk_div<=clk_div;

end

end

always@(posedge clk_div or negedge RSTn) //State Machine

begin

if(!RSTn)

begin

state <= idle;

lcd_data <= 8'bzzzzzzzz;

char_cnt <= 5'd0;

end

else

begin

case(state)

idle: begin state <= clear;

lcd_data <= 8'bzzzzzzzz;

end

clear: begin state <= set_function;

lcd_rs<=1'b0;

lcd_data <= 8'b00000001;

end

set_function: begin

state <= switch_mode;

lcd_rs<=1'b0;

lcd_data <= 8'b00111000;

end

switch_mode: begin

state <= set_mode;

lcd_rs<=1'b0;

lcd_data <= 8'b00001100;

end

set_mode:begin state <= shift;

lcd_rs<=1'b0;

lcd_data <= 8'b00000110;

end

shift: begin state <= set_ddram1;

lcd_rs<=1'b0;

lcd_data <= 8'b0001_0000;

end

set_ddram1:

begin

state <= write_ram1;

lcd_rs<=1'b0;

lcd_data <= 8'b1000_0000;//Line1

end

set_ddram2: begin

state <= write_ram2;

lcd_rs<=1'b0;

lcd_data <= 8'b1100_0000;//Line2

end

write_ram1:

begin

if(char_cnt <=5'd15) //5'd15这个坐标我做了修改

begin

char_cnt <= char_cnt + 1'b1;

lcd_rs<=1'b1;

lcd_data <= data_disp;

state <= write_ram1;

end

else

begin

state <= set_ddram2;

end

end

write_ram2:

begin

if(char_cnt <=5'd30) //5'd30这个坐标我做了修改

begin

char_cnt <= char_cnt + 1'b1;

lcd_rs<=1'b1;

lcd_data <= data_disp;

state <= write_ram2;

end

else

begin

char_cnt <=5'd0;

state <= shift;

end

end

default: state <= idle;

endcase

end

end

always @(char_cnt)

begin

case (char_cnt)

5'd2: data_disp = "D";

5'd3: data_disp = "S";

5'd4: data_disp = "1";

5'd5: data_disp = "3";

5'd6: data_disp = "0";

5'd7: data_disp = "2";

5'd9: data_disp = "C";

5'd10: data_disp = "L";

5'd11: data_disp = "O";

5'd12: data_disp = "C";

5'd13: data_disp = "K";

5'd20: data_disp = Data7+48;

5'd21: data_disp = Data6+48;

5'd22: data_disp = ":";

5'd23: data_disp = Data4+48;

5'd24: data_disp = Data3+48;

5'd25: data_disp = ":";

5'd26: data_disp = Data1+48;

5'd27: data_disp = Data0+48;

default : data_disp =" ";

endcase

end

endmodule

其余代码省略,参考进程10

运行结果,可以发现LCD内容要比LED数码管内容显示时间要慢大约0.5秒,可能是因为LCD的是慢扫描器件所致。

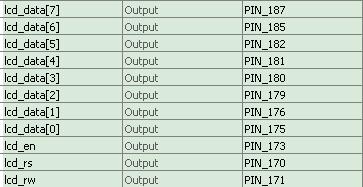

LCD1602 I/O分配图

点击下载DS1302.rar

我要赚赏金

我要赚赏金