代码:

驱动代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee. std_logic_arith.all;

use ieee. std_logic_unsigned.all;

entity fengmq is

port (clk: in std_logic;

fmq: out std_logic

);

end fengmq;

architecture behave of fengmq is

--signal count: std_logic;

begin

process (clk)

begin

if clk'event and clk='1' then

-- count<=clk;

end if;

end process ;

fmq<=clk;

end behave ;

分频代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

entity fp2k is

port(clk_48MHZ: in std_logic;

clk_2KHZ: out std_logic

);

end fp2k;

architecture behav of fp2k is

signal clk_2KHZ_r: std_logic;

signal count : std_logic_vector(14 downto 0);

begin

process (clk_48MHZ)

begin

if clk_48MHZ'event and clk_48MHZ='1' then

if count="110000110100111"then

count<=(others=>'0');

clk_2KHZ_r<=not clk_2KHZ_r;

else count<=count+1;

clk_2KHZ<=clk_2KHZ_r;

end if;

end if;

end process;

end behav;

电路图:

数字时钟代码:

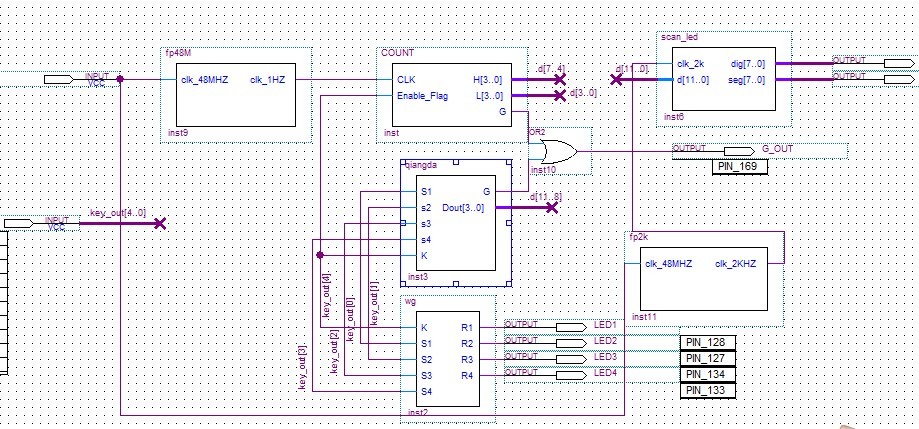

总图:

主程序:实现分秒时功能,对于分秒时可以分三个模块编写,这里把这三个模块放在一起:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity Counter_m_f_s is

port

(

clk,reset : in std_logic ;

bcd_h_m : out std_logic_vector(3 downto 0); --秒钟个位输出

bcd_l_m : out std_logic_vector(3 downto 0); --秒钟十位输出

bcd_l_f : out std_logic_vector(3 downto 0); --分钟个位输出

bcd_h_f : out std_logic_vector(3 downto 0); --分钟十位输出

bcd_l_s : out std_logic_vector(3 downto 0); --时钟个位输出

bcd_h_s : out std_logic_vector(3 downto 0); --时钟十位输出

up : out std_logic

);

end Counter_m_f_s ;

architecture behav of Counter_m_f_s is

signal bcd_h_m_r : std_logic_vector(3 downto 0); --秒钟个位内部信号

signal bcd_l_m_r : std_logic_vector(3 downto 0); --秒钟十位内部信号

signal bcd_h_f_r : std_logic_vector(3 downto 0); --分钟个位内部信号

signal bcd_l_f_r : std_logic_vector(3 downto 0); --分钟十位内部信号

signal bcd_h_s_r : std_logic_vector(3 downto 0); --时钟个位内部信号

signal bcd_l_s_r : std_logic_vector(3 downto 0); --时钟个位内部信号

signal up_r1 : std_logic;

signal up_r2 : std_logic;

begin

U1: process (clk, reset) --秒钟

begin

--if reset='0' then

-- bcd_h_m_r <="0000"; bcd_l_m_r <="0000"; up_r1 <='0';

--else

if clk'event and clk='1' then

if bcd_h_m_r ="0101" and bcd_l_m_r ="1001" then

bcd_h_m_r <="0000"; --59秒,分钟进一

bcd_l_m_r <="0000";

up_r1 <= '1' ;

else

if bcd_l_m_r(3 downto 0) = "1001" then --秒的个位为9,十位进一,分钟不进为

bcd_l_m_r(3 downto 0)<= "0000" ;

bcd_h_m_r(3 downto 0) <= bcd_h_m_r(3 downto 0) + 1 ;

up_r1 <= '0';

else

bcd_l_m_r(3 downto 0) <= bcd_l_m_r(3 downto 0) + 1 ;

up_r1 <= '0';

end if;

end if;

end if;

--end if;

end process;

bcd_h_m <= bcd_h_m_r;

bcd_l_m <= bcd_l_m_r;

U2: process (up_r1 , reset) --分钟

begin

if reset='0' then

bcd_h_f_r <="0000"; bcd_l_f_r <="0000"; up_r2 <='0';

else

if up_r1'event and up_r1='1' then

if bcd_h_f_r ="0101" and bcd_l_f_r ="1001" then --59分,时钟进一

bcd_h_f_r <="0000";

bcd_l_f_r <="0000";

up_r2 <= '1' ;

else

if bcd_l_f_r(3 downto 0) = "1001" then --分的个位为9,十位进一,时钟不进位

bcd_l_f_r(3 downto 0) <= "0000" ;

bcd_h_f_r(3 downto 0) <= bcd_h_f_r(3 downto 0) + 1 ;

up_r2 <= '0';

else

bcd_l_f_r(3 downto 0) <= bcd_l_f_r(3 downto 0) + 1 ;

up_r2 <= '0';

end if;

end if;

end if;

end if;

end process;

bcd_h_f <= bcd_h_f_r;

bcd_l_f <= bcd_l_f_r;

U3: process ( up_r2 , reset) -- 时钟

begin

if reset='0' then

bcd_h_s_r <="0000"; bcd_l_s_r <="0000"; up <='0';

else

if up_r2'event and up_r2='1' then

if bcd_h_s_r ="0010" and bcd_l_s_r ="0011" then --23时,时钟进一。

bcd_h_s_r <="0000";

bcd_l_s_r <="0000";

up <= '1' ;

else

if bcd_l_s_r(3 downto 0) = "1001" then

bcd_l_s_r(3 downto 0)<= "0000" ;

bcd_h_s_r(3 downto 0) <= bcd_h_s_r(3 downto 0) + 1 ;

up <= '0';

else

bcd_l_s_r(3 downto 0) <= bcd_l_s_r(3 downto 0) + 1 ;

up <= '0';

end if;

end if;

end if;

end if;

end process;

bcd_h_s <= bcd_h_s_r;

bcd_l_s <= bcd_l_s_r;

end architecture behav;

数码管动态驱动 :

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_Arith.ALL;

USE IEEE.STD_LOGIC_Unsigned.ALL;

ENTITY xianshi_led IS

PORT(

clk_1k: IN STD_LOGIC;

d: IN STD_LOGIC_VECTOR(31 DOWNTO 0); --输入要显示的数据

dig: OUT STD_LOGIC_VECTOR(7 DOWNTO 0); --数码管选择输出引脚

seg: OUT STD_LOGIC_VECTOR(7 DOWNTO 0) --数码管段输出引脚

);

END ENTITY;

ARCHITECTURE one OF xianshi_led IS

SIGNAL seg_r: STD_LOGIC_VECTOR(7 DOWNTO 0); --定义数码管输出寄存器

SIGNAL dig_r: STD_LOGIC_VECTOR(7 DOWNTO 0); --定义数码管选择输出寄存器

SIGNAL disp_dat: STD_LOGIC_VECTOR(3 DOWNTO 0); --定义显示数据寄存器

SIGNAL count: STD_LOGIC_VECTOR(2 DOWNTO 0); --定义计数寄存器

BEGIN

dig<=dig_r;

seg<=seg_r;

PROCESS(clk_1k)

BEGIN

IF RISING_EDGE(clk_1k) THEN

count<=count+1;

END IF;

END PROCESS;

PROCESS(clk_1k)

BEGIN

IF RISING_EDGE(clk_1k) THEN

CASE count IS

WHEN "000"=> disp_dat<=d(31 DOWNTO 28); --第一个数码管

WHEN "001"=> disp_dat<=d(27 DOWNTO 24); --第二个数码管

WHEN "010"=> disp_dat<=d(23 DOWNTO 20); --第三个数码管

WHEN "011"=> disp_dat<=d(19 DOWNTO 16); --第四个数码管

WHEN "100"=> disp_dat<=d(15 DOWNTO 12); --第五个数码管

WHEN "101"=> disp_dat<=d(11 DOWNTO 8); --第六个数码管

WHEN "110"=> disp_dat<=d(7 DOWNTO 4); --第七个数码管

WHEN "111"=> disp_dat<=d(3 DOWNTO 0); --第八个数码管

END CASE;

CASE count IS --选择数码管显示位

WHEN "000"=> dig_r<="01111111"; --选择第一个数码管显示

WHEN "001"=> dig_r<="10111111"; --选择第二个数码管显示

WHEN "010"=> dig_r<="11011111"; --选择第三个数码管显示

WHEN "011"=> dig_r<="11101111"; --选择第四个数码管显示

WHEN "100"=> dig_r<="11110111"; --选择第五个数码管显示

WHEN "101"=> dig_r<="11111011"; --选择第六个数码管显示

WHEN "110"=> dig_r<="11111101"; --选择第七个数码管显示

WHEN "111"=> dig_r<="11111110"; --选择第八个数码管显示

END CASE;

END IF;

END PROCESS;

PROCESS(disp_dat)

BEGIN

CASE disp_dat IS

WHEN X"0"=> seg_r<=X"c0";--显示0

WHEN X"1"=> seg_r<=X"f9";--显示1

WHEN X"2"=> seg_r<=X"a4";--显示2

WHEN X"3"=> seg_r<=X"b0";--显示3

WHEN X"4"=> seg_r<=X"99";--显示4

WHEN X"5"=> seg_r<=X"92";--显示5

WHEN X"6"=> seg_r<=X"82";--显示6

WHEN X"7"=> seg_r<=X"f8";--显示7

WHEN X"8"=> seg_r<=X"80";--显示8

WHEN X"9"=> seg_r<=X"90";--显示9

WHEN X"a"=> seg_r<=X"88";--显示a

WHEN X"b"=> seg_r<=X"83";--显示b

WHEN X"c"=> seg_r<=X"c6";--显示c

WHEN X"d"=> seg_r<=X"a1";--显示d

WHEN X"e"=> seg_r<=X"86";--显示e

WHEN X"f"=> seg_r<=X"8e";--显示f

END CASE;

END PROCESS;

END;

另外再加1hz分频和2KHZ分频。

基本要求:

1、主持人按下抢答开关松起后,数码管10秒倒计时,期间哪位选手抢答成功就显示选手号码。

2、如果主持人按下抢答开关还没松起就有人抢答即为违规,对于的LED亮。

3、主持人按键可以对数码管清零。

基本模块:1、倒计时 2、抢答模块 3、led警告违规 4、显示模块

总图:

1、倒计时:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY COUNT IS

PORT (CLK, Enable_Flag: IN STD_LOGIC;

H,L: OUT STD_LOGIC_VECTOR (3 DOWNTO 0);

G:OUT STD_LOGIC); --声音报警

END COUNT;

ARCHITECTURE behave OF COUNT IS

signal HH, LL: STD_LOGIC_VECTOR (3 DOWNTO 0);

BEGIN

PROCESS (CLK, Enable_Flag)

--VARIABLE HH, LL: STD_LOGIC_VECTOR (3 DOWNTO 0);

BEGIN

IF CLK'EVENT AND CLK='1'THEN ---允许抢答

IF Enable_Flag='0'THEN

HH<="0001";

LL<="0000";

else

IF LL=0 AND HH=0 THEN

G<='0';

ELSe

IF LL=0 THEN

LL<="1001";

HH<=HH-1;

ELSE

LL<=LL-1;

END IF;

end if;

--ELSE

--G<='1';

-- HH<="0010";

-- LL<="0000";

END IF;

END IF;

H<=HH;

L<=LL;

END PROCESS;

END behave;

2、抢答模块

library ieee;

use ieee.std_logic_1164.all;

use ieee. std_logic_arith.all;

use ieee. std_logic_unsigned.all;

-------------------------------------------------------------------

entity qiangda is

port( S1,s2,s3,s4 : in std_logic; --输入:表示4个人,为0表示有抢答

K : in std_logic; --主持人抢答开始键

G : out std_logic; --报警信号

Dout : out std_logic_vector(3 downto 0) ); --抢答结果显示

end qiangda;

--------------------------------------------------------------------

architecture behave of qiangda is

signal D : std_logic_vector(3 downto 0);

begin

process(S1,s2,s3,s4,K) --抢答结果显示

begin

if(K='0') then

D<="0000";

else

if(S1='0') then

D<="0001";

G<='0';

else

G<='1';

end if;

if(S2='0') then

D<="0010";

G<='0';

ELSE G<='1';

end if;

if(S3='0') then

D<="0011";

G<='0';

ELSE G<='1';

end if;

if(S4='0') then

D<="0100";

G<='0';

--S1<='1';

-- S2<='1';

-- S3<='1';

ELSE G<='1';

end if;

end if;

end process;

dout<=d;

end behave;

3、led警告违规

LIBRARY ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

ENTITY wg IS

PORT(K: IN std_logic;

S1, S2, S3, S4: IN std_logic;

R1, R2, R3, R4: OUT std_logic); --红色灯指示超前抢答台号

END wg;

ARCHITECTURE a OF wg IS

BEGIN

process(k,s1,s2,s3,s4)

begin

if(K='0') then

if(S1='0') then

R1<='0';

elsif(S2='0') then

R2<='0';

elsif(S3='0') then

R3<='0';

elsif (S4='0') then

R4<='0';

end if;

end if;

if k='1' then

r1<='1';

r2<='1';

r3<='1';

r4<='1';

end if;

end process;

END a;

用8个按键弹出1、2、3、4、5、6、7、1音符

程序如下:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity fenping is

port(clk_50m: in std_logic;

fmq : out std_logic;

key1: in std_logic;

key2: in std_logic;

key3: in std_logic;

key4: in std_logic;

key5: in std_logic;

key6: in std_logic;

key7: in std_logic;

key8: in std_logic

);

end;

architecture behave of fenping is

signal clk_262_r: std_logic;

signal clk_294_r: std_logic;

signal clk_330_r: std_logic;

signal clk_349_r: std_logic;

signal clk_392_r: std_logic;

signal clk_440_r: std_logic;

signal clk_494_r: std_logic;

signal clk_523_r: std_logic;

begin

u1: process (clk_50m)

variable count1: std_logic_vector(16 downto 0);

variable count2: std_logic_vector(16 downto 0);

variable count3: std_logic_vector(16 downto 0);

variable count4: std_logic_vector(16 downto 0);

variable count5: std_logic_vector(16 downto 0);

variable count6: std_logic_vector(16 downto 0);

variable count7: std_logic_vector(16 downto 0);

variable count8: std_logic_vector(16 downto 0);

begin

if clk_50m'event and clk_50m='1' then

if count1=95419 then

count1:=(others=>'0');

clk_262_r<=not clk_262_r;

else

count1:=count1+1;

end if;

end if;

if clk_50m'event and clk_50m='1' then

if count2=84459 then

count2:=(others=>'0');

clk_294_r<=not clk_294_r;

else

count2:=count2+1;

end if;

end if;

if clk_50m'event and clk_50m='1' then

if count3=75757 then

count3:=(others=>'0');

clk_330_r<=not clk_330_r;

else

count3:=count3+1;

end if;

end if;

if clk_50m'event and clk_50m='1' then

if count4=71633 then

count4:=(others=>'0');

clk_349_r<=not clk_349_r;

else

count4:=count4+1;

end if;

end if;

if clk_50m'event and clk_50m='1' then

if count5=63776 then

count5:=(others=>'0');

clk_392_r<=not clk_392_r;

else

count5:=count5+1;

end if;

end if;

if clk_50m'event and clk_50m='1' then

if count6=56818 then

count6:=(others=>'0');

clk_440_r<=not clk_440_r;

else

count6:=count6+1;

end if;

end if;

if clk_50m'event and clk_50m='1' then

if count7=50607 then

count7:=(others=>'0');

clk_494_r<=not clk_494_r;

else

count7:=count7+1;

end if;

end if;

if clk_50m'event and clk_50m='1' then

if count8=47801 then

count8:=(others=>'0');

clk_523_r<=not clk_523_r;

else

count8:=count8+1;

end if;

end if;

end process;

u2:process(key1,key2,key3,key4,key5,key6,key7,key8)

begin

if key1='0'then

fmq<=clk_262_r;

end if;

if key2='0'then

fmq<=clk_294_r;

end if;

if key3='0'then

fmq<=clk_330_r;

end if;

if key4='0'then

fmq<=clk_349_r;

end if;

if key5='0'then

fmq<=clk_392_r;

end if;

if key6='0'then

fmq<=clk_440_r;

end if;

if key7='0'then

fmq<=clk_494_r;

end if;

if key8='0'then

fmq<=clk_523_r;

end if;

end process;

end;

.SOF文件http://share.eepw.com.cn/share/download/id/79562

回复

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 基于ArduinoUNO开发板的AT24C02读写测试被打赏¥16元 | |

| TCS3472S传感器及其色彩检测被打赏¥19元 | |

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |

谢谢哦,啸风!

谢谢哦,啸风!