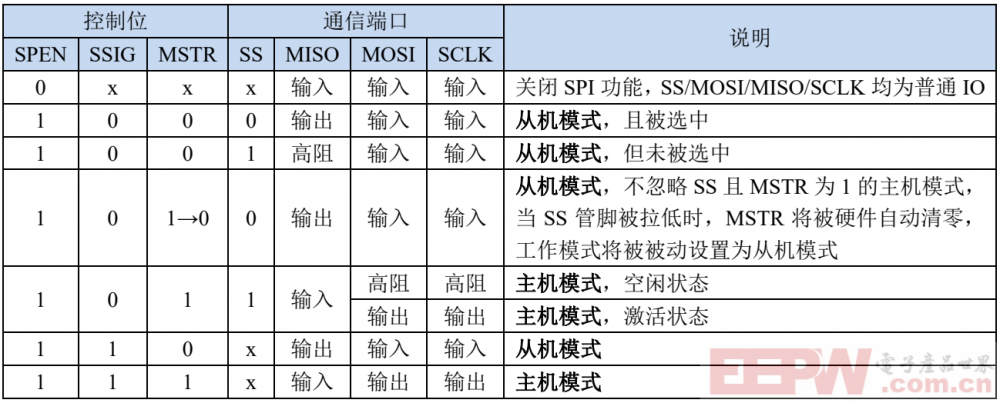

SPI外设可以工作在主机模式或者从机模式。在通讯过程中相关引脚的状态:

一、从机模式的注意事项:

当 CPHA=0 时,SSIG 必须为 0(即不能忽略 SS 脚)。在每次串行字节开始还发送前 SS 脚必须拉

低,并且在串行字节发送完后须重新设置为高电平。SS 管脚为低电平时不能对 SPDAT 寄存器执行写操

作,否则将导致一个写冲突错误。CPHA=0 且 SSIG=1 时的操作未定义。

当 CPHA=1 时,SSIG 可以置 1(即可以忽略脚)。如果 SSIG=0,SS 脚可在连续传输之间保持低

有效(即一直固定为低电平)。这种方式适用于固定单主单从的系统。

二、主机模式的注意事项:

在 SPI 中,传输总是由主机启动的。如果 SPI 使能(SPEN=1)并选择作为主机时,主机对 SPI 数据

寄存器 SPDAT 的写操作将启动 SPI 时钟发生器和数据的传输。在数据写入 SPDAT 之后的半个到一个 SPI

位时间后,数据将出现在 MOSI 脚。写入主机 SPDAT 寄存器的数据从 MOSI 脚移出发送到从机的 MOSI

脚。同时从机 SPDAT 寄存器的数据从 MISO 脚移出发送到主机的 MISO 脚。

传输完一个字节后,SPI 时钟发生器停止,传输完成标志(SPIF)置位,如果 SPI 中断使能则会产

生一个 SPI 中断。主机和从机 CPU 的两个移位寄存器可以看作是一个 16 位循环移位寄存器。当数据从

主机移位传送到从机的同时,数据也以相反的方向移入。这意味着在一个移位周期中,主机和从机的数

据相互交换。

三、通过 SS 改变模式

如果 SPEN=1,SSIG=0 且 MSTR=1,SPI 使能为主机模式,并将 SS 脚可配置为输入模式化或准双

向口模式。这种情况下,另外一个主机可将该脚驱动为低电平,从而将该器件选择为 SPI 从机并向其发

送数据。为了避免争夺总线,SPI 系统将该从机的 MSTR 清零,MOSI 和 SCLK 强制变为输入模式,而

MISO 则变为输出模式,同时 SPSTAT 的 SPIF 标志位置 1。

用户软件必须一直对 MSTR 位进行检测,如果该位被一个从机选择动作而被动清零,而用户想继续

将 SPI 作为主机,则必须重新设置 MSTR 位,否则将一直处于从机模式。

四、写冲突

SPI 在发送时为单缓冲,在接收时为双缓冲。这样在前一次发送尚未完成之前,不能将新的数据写

入移位寄存器。当发送过程中对数据寄存器 SPDAT 进行写操作时,WCOL 位将被置 1 以指示发生数据

写冲突错误。在这种情况下,当前发送的数据继续发送,而新写入的数据将丢失。

当对主机或从机进行写冲突检测时,主机发生写冲突的情况是很罕见的,因为主机拥有数据传输的

完全控制权。但从机有可能发生写冲突,因为当主机启动传输时,从机无法进行控制。

接收数据时,接收到的数据传送到一个并行读数据缓冲区,这样将释放移位寄存器以进行下一个数

据的接收。但必须在下个字符完全移入之前从数据寄存器中读出接收到的数据,否则,前一个接收数据

将丢失。

WCOL 可通过软件向其写入“1”清零。

我要赚赏金

我要赚赏金