CMX264是CML公司推出的用于话音通信系统的频域扰频芯片,片上有4个可编程的扰频频率点,以选定的频率为中心,将话音信号的频谱切割成两段并分别倒置;接收端将上述过程进行反变换,还原出原始语音信号,从而达到加密的目的。

本文设计了一种基于CMX264,用于集群系统话音扰频的方案,通过引入无线数传技术和跳频概念,在不增加设备复杂度的情况下,保障网内通话的安全性和应用范围。

1 方案对比

1.1 单一扰频方式

在固定扰频点上实施扰频,这种方案设计简单,且不受中继台影响,缺点是容易被破解。

1.2 跳频扰频

通过单片机进行控制和定时,在提供的四个扰频点中按照约定的次序和时间间隔进行切换,类似跳频通信技术,只是跳动的不是载波频率,而是扰频点频率。与单一扰频方式相比,该方案安全性能有所提高,但不适于大网络,因为信号经过中继台以后会引入延时,导致跳频不同步,且跳频方式相对固定,仍有一定的安全隐患。

1.3 结合数传技术的跳频扰频

针对以上两者的不足,提出了结合数传技术的跳频扰频方案。该方案在模拟系统上实现数据传输,每次通话前先发送跳频信令,即本次跳频的次序以及时间间隔,由扰频信令确定起跳时间,克服了中继台的延时影响;跳频次序的随机性,加大了窃听的难度。

2 系统设计

系统原理如图1,选用ATMEGA8单片机进行控制和编码,CMX264进行话音扰频,MSM6882无线MODEM完成数据的调制解调,高莱 (Golay)码进行信道纠错,通过扰频信令确定跳频方式。呼叫方每次通话前,即按下PTT之后,在单片机控制下先由MSM6882发送扰频信令,确定此次通话是否扰频以及扰频的次序和时间间隔,CMX264按照约定的规则改变扰频点,接收方根据解调出的扰频信令设置起跳时间和方式,达到同步接收的效果。

2.1 CMX264的设计

话音信号的频率范围是 300Hz~3 300Hz,CMX264选择四个频点中的一个,将话音信号划分为两个子带,并分别对子带的频谱进行倒置,接收端再进行反变换还原出原始语音信号。当晶振频率为4.433 619MHz时,四个扰频点频率分别为1 027Hz、1 276Hz、1 482Hz和1 966Hz。话音信号由MICIN端进入,经过扰频、加重处理后由MICO端输出;射频接收解调出的话音信号由RXIN端进入,经去扰频、加重处理后由 EXTO端输出。可见CMX264只是串接在原有的话音通路中改变频谱结构而不影响传输效果。

CMX264提供串行接口来控制内部状态和工作模式,指令的功能包括:省电模式、是否扰频、话音输入输出控制、预加重/去加重选择和扰频点选择。指令的格式定义如表1所示。

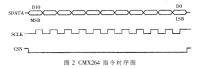

数据通过DATA端按高位在前的顺序写入,在SCLK端的上升沿锁存数据,CSN端提供片选信号。CMX264处在从接收的位置,单片机只需根据时序定义,通过I/O口即可实现此串行接口的功能,对CMX264进行控制。时序如图2所示。

2.2 无线数传模块设计

2.2.1 MODEM的设计

电台内部针对话音频带进行了带通滤波,因此对MODEM调制后的信号有频率限制,不能超出话音频率范围。MSM6882是OKI公司推出的MSK全双工调制解调器,MSK信号包络恒定,具有最小功率谱占用率,在码元转换瞬间没有相位突变,数据传输波特率可以在1 200/2 400进行选择,载波频率600~2400Hz,因此完全可以通过电台的话音信道进行传输。

MSM6882内部提供接收时钟RT和发送时钟ST,通过同步串口与单片机通信,单片机使用外部中断模拟实现同步串口的功能。

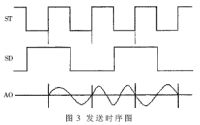

发送数据时,单片机输出的数据SD在ST上升沿被锁存,因此将ST与单片机的外部中断INT0相连,INT0设置为下降沿触发,单片机在中断处理程序中改变SD电平,数字信号经过内部调制后产生MSK信号输出AO,发送时序如图3所示。

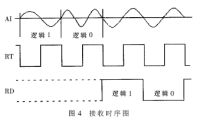

接收数据时,输入AI的MSK信号经过内部滤波器后可恢复为串行数据输出,同时从接收的数据中还可恢复出同步时钟RT,将RT与单片机的外部中断INT1相连,中断设置为上升沿触发,单片机在中断处理程序中读取RD电平值。接收时序如图4所示。

2.2.2 纠错编码的设计

移动通信时必然要受到无线信道传输特性的不理想以及加性噪声的影响,要在这样的传播条件下保持可以接受的传输质量,就必须采取各种技术措施来抵消衰落的不利影响,信道纠错编码就是其中一种有效的抗衰落技术。

由于扰频信令的信息非常重要,而且要求有实时性,只有检错重发并不能满足要求。针对单片机系统的特点和编解码的复杂度,纠错编码采用Golay码。 Golay码是一种特殊的非本原BCH码,属于前向纠错编码FEC(Forward Error Correction),也是目前为止发现的惟一能纠正多个错误的完备码,因其在噪声环境下具有良好的纠错性能而获得了广泛应用,尤其适合短码字长和短处理时延的应用场合。

本方案选用的Golay(24,12)码最小距离为8,能纠正3个随机错误同时检测4个错误。针对8位单片机的特点,将信息位缩短为8bit,并在最后添加0101进行帧同步码的提取,最终构成3个字节的完整结构,提高了单片机编码的效率。编解码的程序全部用C语言实现,程序复杂度适中,Atmega8单片机的运算能力完全可以胜任。Golay码结构如表2所示。

2.2.3 数据帧结构的设计

MSM6882接收的数据是与时钟同步的比特流,为了从所接收的数据中提取时钟信号,首先发送6字节即48bit“1”和“0”交替出现的位同步码。为了按字节接收数据,确定每一帧的起始位,需要在比特流中添加帧同步信息,以避免帧同步图案与数据中内容相同而导致的误判。根据所选用的纠错编码特点,每组Golay码三个字节的最后4个 bit为0101,即不会出现三个字节以上的连续0或者连续1,所以帧起始码选用31bit1和1bit0,帧结束码采用32bit连0。在接收中断处理程序中,检测到31bit1和1bit0就开始按字节接收数据,此后每3个字节一组进行纠错解码,同时开始对接收到的连续0进行计数,超过32个就认为一帧接收完毕。帧结构如表3所示。

2.2.4 数传模块程序的设计

数传程序主要实现编码和发送数据、接收数据和解码的功能。发送时,Golay编码由一个字节变为三个字节,把待发送数组先全部编码再进行发送;接收时,先将三个字节一组的字节流存储为数组,再进行Golay解码,这样,将占用大量RAM空间和时间。为了节省单片机资源,提高程序执行效率,把编码与发送数据、接收数据与解码结合起来同时进行。

首先,定义全局变量作为接收发送的计数器和状态标志位,主函数中循环查询系统工作状态确定是否进行编码或者解码和启动发送字节的子函数;在中断处理函数中每接收和发送完一个字节,就改变相应的计数器和状态标志位,供主函数查询。这样把编解码与收发结合起来,提高了程序的执行效率,缩短了程序运行的时间。

其次,接收和发送都设置双缓冲区,结构定义代码如下:

typedef struct

{

unsigned char rc; /*信息字节*/

unsigned int r1; /*校验字*/

}Golay;

Golay RecvBuffer[2];

Golay SendBuffer[2];

在中断处理函数中发送一个缓冲区数据的同时,在主函数里编码填充另一缓冲区;在中断处理函数中接收数据、填充一个缓冲区时,在主函数里对另一个缓冲区中接收的上一组数据进行解码。在中断处理函数中改变全局的状态标志位,在主函数里进行缓冲区间的切换。通过设置双缓冲区,收发分别只需占用两组编码空间,节省了单片机的RAM资源。

2.3 扰频信令的设计

每次通话之前,即按下PTT之后,首先延时一段时间,这个时间由中继台的最大延时决定;再发送扰频信令,确定此次通话是否扰频以及扰频的次序和时间间隔,为了与未加扰频模块的手持台通信,需要保留不扰频的功能,即CMX264在Clear模式下工作;同时增加地址选项,通过地址进行分组,可以实现组呼和单呼;通话完毕时发送结束帧,使手持台恢复到Clear 模式。根据上述要求,设计扰频信令格式如表4所示。

结构定义代码如下:

typedef struct

{

unsigned char ScrambleFrameType; /*帧类型*/

unsigned char RecvAddress[2]; /*接收地址*/

unsigned char ScrambleSeq[4]; /*扰频次序*/

unsigned char HopCyc; /*时间间隔*/

}Scramble;

本文介绍的方案主要针对使用模拟集群的专用网络,调度通话内容需要保密以避免窃听和干扰。本方案通过电台的话音信道进行无线数据传输,对传统扰频方式进行了改进,提高了系统的安全性和应用范围。

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 基于ArduinoUNO开发板的AT24C02读写测试被打赏¥16元 | |

| TCS3472S传感器及其色彩检测被打赏¥19元 | |

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |