共7条

1/1 1 跳转至页

请问IDE(ATA)硬盘引脚的逻辑电平是多少?

2楼

LVTTL是3.3V的,IDE是5V的。3.3V驱动5V是可以的,关键在于你的FPGA是否可以承受5V电压,如果不能,加个245做个电平转换

4楼

FPGA 3.3V的IO不能长时间承受5V。

你的IDE接口上要接的是硬盘,还是IDE电子盘,我知道有很多电子盘的VCC是5V和3V可选的。

如果必须要接5V的话,还是要接245做保护的,把V4的IO烧了,划不着。

如果板子做好了,可以专门做个转接板

你的IDE接口上要接的是硬盘,还是IDE电子盘,我知道有很多电子盘的VCC是5V和3V可选的。

如果必须要接5V的话,还是要接245做保护的,把V4的IO烧了,划不着。

如果板子做好了,可以专门做个转接板

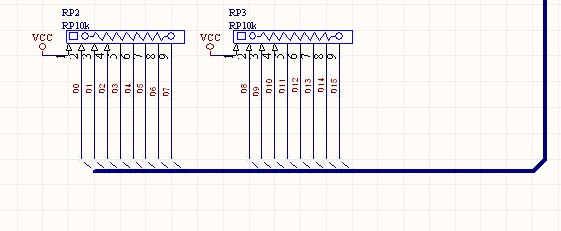

我用的是IDE的移动硬盘。如果不做转换电路,用别的方案行不行?我查了下,通过FPGA内部逻辑来设计端接电阻,或者设置上拉电阻http://iknow.baidu.com/question/109170552.html,不知是否好使?

我程序调了段时间没什么结果,不知道FPGA芯片是不是已经损坏了,有没有什么好的方法做下测试啊?

我程序调了段时间没什么结果,不知道FPGA芯片是不是已经损坏了,有没有什么好的方法做下测试啊?

6楼

那不还是要改板子吗?那么多线,串电阻或并电阻都不好弄。还是做个转接版,用IDE线连接两个板子。

想试试FPGA是否完好,写个简单的逻辑试试不就知道了吗。要是真把V2烧了,那就杯具了

想试试FPGA是否完好,写个简单的逻辑试试不就知道了吗。要是真把V2烧了,那就杯具了

共7条

1/1 1 跳转至页

回复

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 基于ArduinoUNO开发板的AT24C02读写测试被打赏¥16元 | |

| TCS3472S传感器及其色彩检测被打赏¥19元 | |

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |