我用quartusII的megawizard生成了一个锁相环,请问怎么用moelsim来仿真?

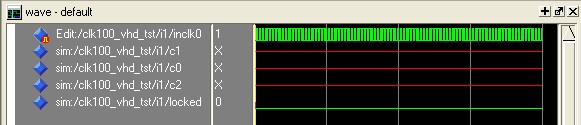

我把库编译好了,然而仿真时输出是不定态,如下图所示。我觉得不应该是输出还没有锁定,因为我的输入时钟周期是20ns的,而我仿真时长为2us,不可能还没锁定,而且即使没有锁定也不该是不定态,也是有输出的,请问是怎么回事呢?

我自己新建了一个工程:Quartus II V9.1, Modelsim SE 6.5C, EP2C35F672C6, Verilog

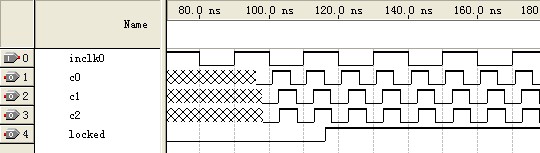

Modelsim下做行为仿真,结果正确:

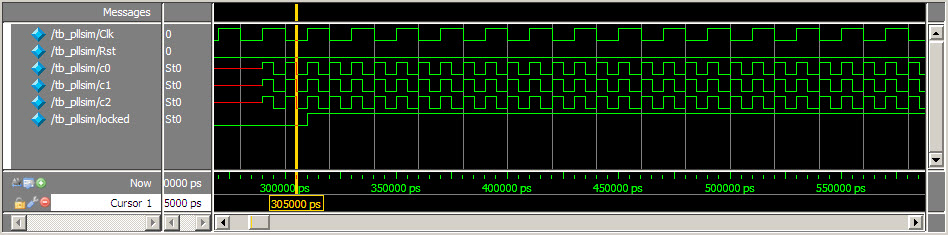

Quartus II下仿真结果和你的一样。

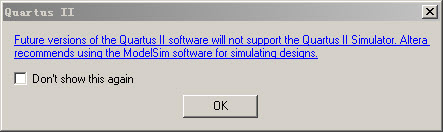

Quartus II做仿真时有提示如下:

我想应该就是这个原因。看来Altera打算放弃自己的Simulator了。

如果需要的话,我可以把工程上传。

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 基于ArduinoUNO开发板的AT24C02读写测试被打赏¥16元 | |

| TCS3472S传感器及其色彩检测被打赏¥19元 | |

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |