5.5 FPGA相关电路设计知识

FPGA的相关电路主要就是FPGA的配置电路,其余的应用电路只要将外围芯片连接到FPGA的通用I/O管脚上即可。

5.5.1 配置电路

FPGA配置方式灵活多样,根据芯片是否能够自己主动加载配置数据分为主模式、从模式以及JTAG模式。典型的主模式都是加载片外非易失( 断电不丢数据) 性存储器中的配置比特流,配置所需的时钟信号( 称为CCLK) 由FPGA内部产生,且FPGA控制整个配置过程。从模式需要外部的主智能终端( 如处理器、微控制器或者DSP等) 将数据下载到FPGA中,其最大的优点就是FPGA 的配置数据可以放在系统的任何存储部位,包括:Flash、硬盘、网络,甚至在其余处理器的运行代码中。JTAG 模式为调试模式,可将PC 中的比特文件流下载到FPGA中,断电即丢失。此外,目前赛灵思还有基于Internet 的、成熟的可重构逻辑技术System ACE解决方案。

(1) 主模式

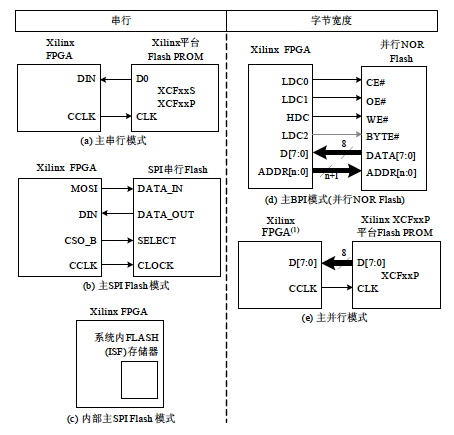

在主模式下,FPGA上电后,自动将配置数据从相应的外存储器读入到SRAM中,实现内部结构映射;主模式根据比特流的位宽又可以分为:串行模式( 单比特流) 和并行模式( 字节宽度比特流) 两大类。如:主串行模式、主SPI Flash 串行模式、内部主SPI Flash串行模式、主BPI 并行模式以及主并行模式,如图5-19所示。

(2) 从模式

在从模式下,FPGA 作为从属器件,由相应的控制电路或微处理器提供配置所需的时序,实现配置数据的下载。从模式也根据比特流的位宽不同分为串、并模式两类,具体包括:从串行模式、JTAG模式和从并行模式三大类,其概要说明如图5-20所示。

(3)JTAG模式

在JTAG模式中,PC和FPGA通信的时钟为JTAG接口的TCLK,数据直接从TDI进入FPGA,完成相应功能的配置。

图5-19 常用主模式下载方式示意图

图5-20 常用的从模式下载方式示意图

目前,主流的FPGA芯片都支持各类常用的主、从配置模式以及JTAG,以减少配置电路失配性对整体系统的影响。在主配置模式中,FPGA自己产生时钟,并从外部存储器中加载配置数据,其位宽可以为单比特或者字节;在从模式中,外部的处理器通过同步串行接口,按照比特或字节宽度将配置数据送入FPGA芯片。此外,多片FPGA可以通过JTAG菊花链的形式共享同一块外部存储器,同样一片/ 多片FPGA也可以从多片外部存储器中读取配置数据以及用户自定义数据。

Xilinx FPGA的常用配置模式有5 类:主串模式、从串模式、Select MAP模式、Desktop配置和直接SPI配置。在从串配置中,FPGA接收来自于外部PROM或其它器件的配置比特数据,在FPGA产生的时钟CCLK的作用下完成配置,多个FPGA可以形成菊花链,从同一配置源中获取数据。Select MAP模式中配置数据是并行的,是速度最快的配置模式。SPI配置主要在具有SPI接口的FLASH电路中使用。下面以Spartan-3E系列芯片为例,给出各种模式的配置电路。

5.5.2 主串模式——最常用的FPGA配置模式

1.配置单片FPGA

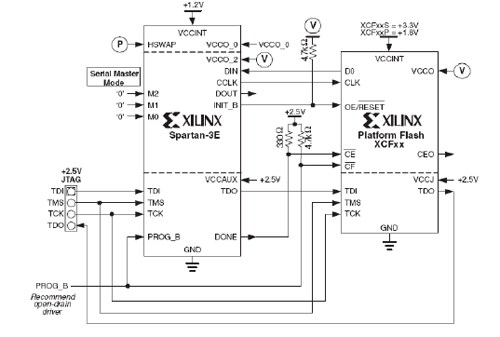

在主串模式下,由FPGA的CCLK管脚给PROM提供工作时钟,相应的PROM在CCLK的上升沿将数据从D0管脚送到FPGA的DIN管脚。无论PROM芯片类型( 即使其支持并行配置),都只利用其串行配置功能。Spartan3E系列FPGA的单片主串配置电路如图5-21所示。主串模式是赛灵思公司各种配置方式中最简单,也最常用的方式,基本所有的可编程芯片都支持主串模式。

图5-21 Spartan-3E主串模式配置电路

2.配置电路的关键点

主串配置电路最关键的3点就是JTAG链的完整性、电源电压的设置以及CCLK信号的考虑。只要这3步任何一个环节出现问题,都不能正确配置PROM芯片。

(1)JTAG链的完整性

FPGA和PROM芯片都有自身的JTAG接口电路,所谓的JTAG链完整性指的是将JTAG连接器、FPGA、PROM的TMS、TCK连在一起,保证从JTAG连接器TDI到其TDO之间,形成JTAG连接器的“TDI →(TDI~TDO) → (TDI~TDO) → JTAG连接器TDO”的闭合回路,其中(TDI~TDO) 为FPGA或者PROM芯片自身的一对输入、输出管脚。图5-12中配置电路的JTAG链从连接器的TDI到FPGA的TDI,再从FPGA的TDO到PROM的TDI,最后从PROM的TDO到连接器的TDO,形成了完整的JTAG链,FPGA芯片被称为链首芯片。也可以根据需要调换FPGA和PROM的位置,使PROM成为链首芯片。

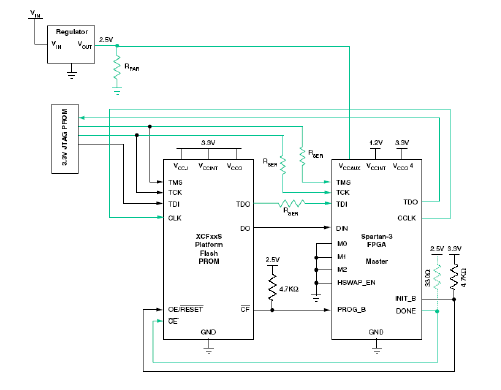

(2) 电源适配性

如图5-22所示,由于FPGA和PROM要完成数据通信,二者的接口电平必须一致,即FPGA相应分组的管脚电压Vcco_2必须和PROM Vcco的输入电压大小一致,且理想值为2.5V,这是由于FPGA的PROG_B和DONE管脚由2.5V的Vccaux供电。此外,由于JTAG连接器的电压也由2.5V的Vccaux提供,因此PROM的VCCJ也必须为2.5V。因此,如果接口电压和参考电压不同,在配置阶段需要将相应分组的管脚电压和参考电压设置为一致;在配置完成后,再将其切换到用户所需的工作电压。当然,FPGA和PROM也可以自适应3.3V的I/O电平以及JTAG电平,但需要进行一定的改动,即添加几个外部限流电阻,如图5-22所示。在主串模式下,XCFxxS系列PROM的核电压必须为3.3V,XCFxxP系列PROM的核电压必须为1.8V。

图5-22 3.3V的JTAG配置电路示意图

图5-22中的RSER、RPAR这两个电阻要特别注意。首先,RSER= 68Ω将流入每个输入的电流限制到9.5mA ;其次,N= 3三个输入的二极管导通,

RPAR = VCCAUX min/ NIIN = 2.375V/(3*9.5mA)

=83 Ω或82 Ω ( 与标准值误差小于5%的电阻 )

(3)CCLK的信号完整性

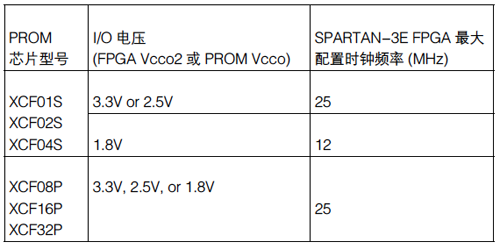

CCLK信号是JTAG配置数据传输的时钟信号,其信号完整性非常关键。FPGA 配置电路刚开始以最低时钟工作,如果没有特别指定,将逐渐提高频率。CCLK信号是由FPGA内部产生的,对于不同的芯片和电平,其最大值如表F-1所示。

表5-1 不同PROM芯片的最大配置时钟频率

3.配置多片FPGA

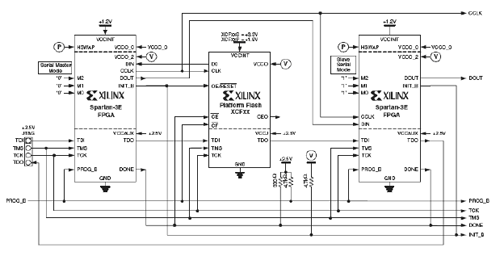

多片FPGA的配置电路和单片的类似,但是多片FPGA之间有主(Master)、从(Slave) 之分,且需要选择不同的配置模式。两片Spartan 3E系列FPGA的典型配置电路如图5-23所示,两片FPGA存在主、从地位之分。

图5-23 主从模式下两片FPGA的配置电路

我要赚赏金

我要赚赏金