共6条

1/1 1 跳转至页

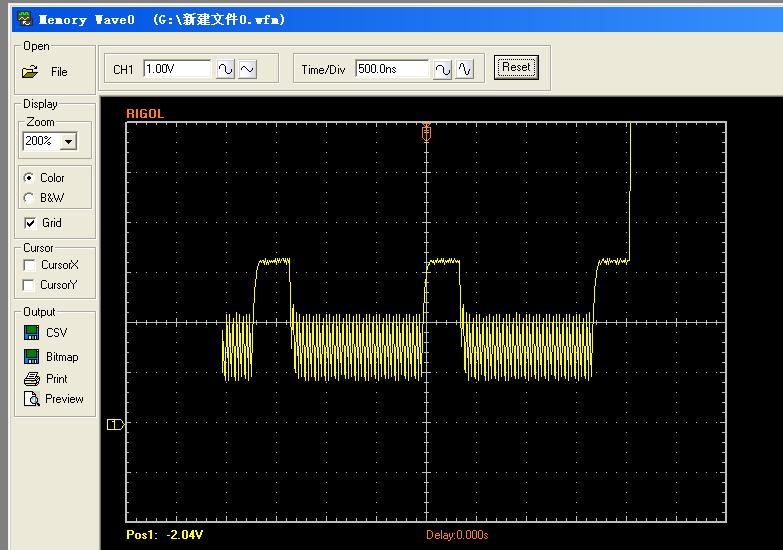

求助:谁能帮我看看这个波形,低电平在2.2V到0.8V之间,可能是什麽原因引起的?

看了下白皮书,http://www.docin.com/p-181173818.html这个文件第60页,里面好象说只是一个从SPI,SLK应该有主SPI提供,去读字库的话,是两个从SPI连接,没有人提供是SLK时钟

共6条

1/1 1 跳转至页

我要赚赏金

我要赚赏金