Veiko的FPGA开发进程贴

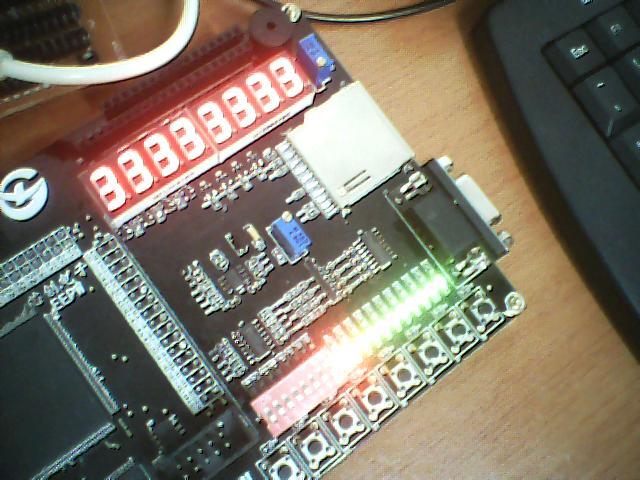

相机也不得行,图是用电脑摄相头照的,大虾们就将就将就哈,

重要的是结果出来了!

重要的是结果出来了!| 2012-10-25 | 实验1 点亮LED灯 | forum.eepw.com.cn/thread/221032/1 #5 |

| 2012-10-25 | 实验2:系统时钟分频使LED闪烁 | forum.eepw.com.cn/thread/221032/1 #6 |

| 2012-10-25 | 实验3:流水灯 | forum.eepw.com.cn/thread/221032/1 #7 |

| 2012-10-31 | 数码管实验1:数码管静态显示 | forum.eepw.com.cn/thread/221032/1 #8 |

| 2012-11-1 | 数码管实验2:与拨码开关的实验 | forum.eepw.com.cn/thread/221032/2 #11 |

| 2012-11-7 | 数码管实验3:动态显示秒表 | forum.eepw.com.cn/thread/221032/2 #12 |

| 2012-11-7 | 数码管按键实验1:数字跑表 | forum.eepw.com.cn/thread/221032/2 #13 |

| 2012-11-8 | 蜂鸣器实验:电子琴 | forum.eepw.com.cn/thread/221032/2 #14 |

| 2012-11-10 | 用TCl脚本对FPGA引脚进行配置 | forum.eepw.com.cn/thread/221032/2 #15 |

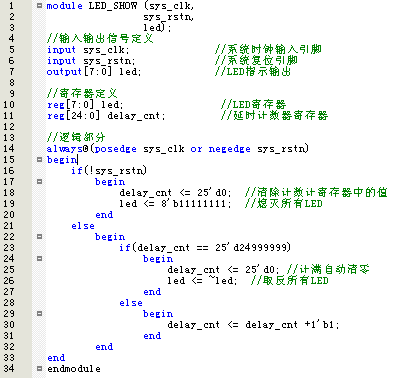

实验3:流水灯

代码:

module LS_LED (sys_clk,

sys_rstn,

led);

input sys_clk;

input sys_rstn;

output[10:0] led;

reg[24:0] delay_cnt;

reg[10:0] led;

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

begin

delay_cnt <= 25'd0;

led <= 11'b11111111111;

end

else

begin

if(delay_cnt == 25'd24999999)

begin

delay_cnt <= 25'd0;

if(led == 11'b11111111111)

begin

led <= 11'b11111111110;

end

if(led == 11'b11111111110)

begin

led <= 11'b11111111101;

end

if(led == 11'b11111111101)

begin

led <= 11'b11111111011;

end

if(led == 11'b11111111011)

begin

led <= 11'b11111110111;

end

if(led == 11'b11111110111)

begin

led <= 11'b11111101111;

end

if(led == 11'b11111101111)

begin

led <= 11'b11111011111;

end

if(led == 11'b11111011111)

begin

led <= 11'b11110111111;

end

if(led == 11'b11110111111)

begin

led <= 11'b11101111111;

end

if(led == 11'b11101111111)

begin

led <= 11'b11011111111;

end

if(led == 11'b11011111111)

begin

led <= 11'b10111111111;

end

if(led == 11'b10111111111)

begin

led <= 11'b01111111111;

end

if(led == 11'b01111111111)

begin

led <= 11'b11111111110;

end

end

else

begin

delay_cnt <= delay_cnt + 1'b1;

end

end

end

endmodule

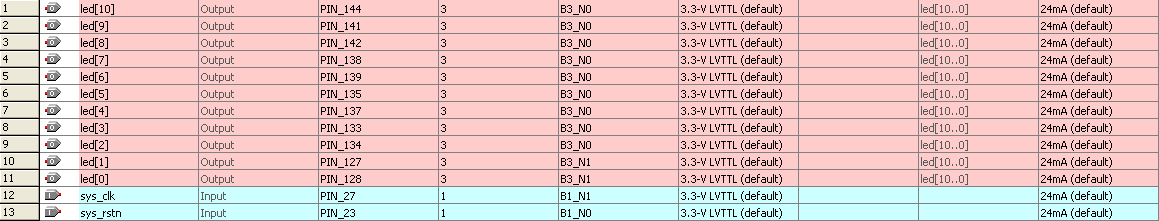

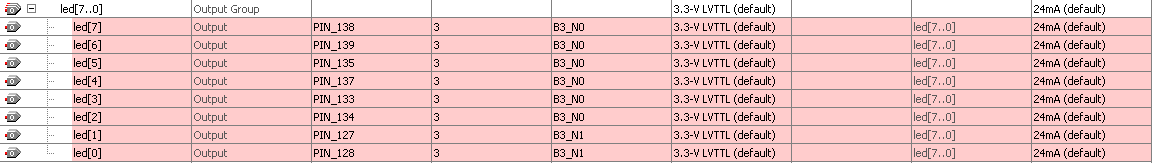

引脚分布:

效果照片:

感觉Verilog比起VHDL好像是要简单得多,就不知道后面的内容怎么样了……

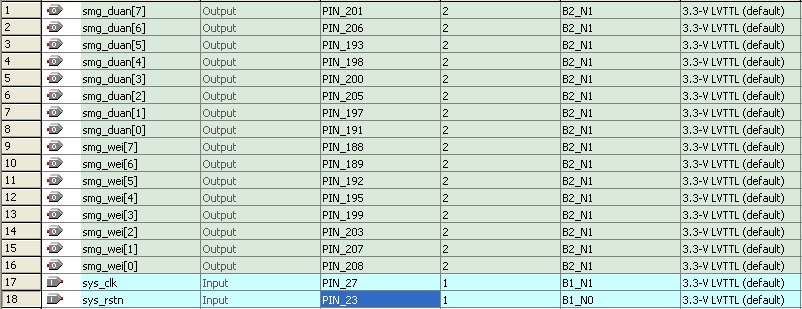

数码管显示实验一:数码管静态显示

工程文件:

share.eepw.com.cn/share/download/id/79258

回复

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |

| 【S32K3XX】LIN 通讯模块使用被打赏¥31元 | |

| 【FreeRtos】FreeRtos + MPU模块的配置使用被打赏¥32元 | |

:

: