最基本的几个输入输出设备测试完成,另外的功能暂时不打算实验。下一步计划是以系统总体设计进行实验。

需要构建Nios II软核,编写app实验程序。

由于免费的Quartus II版本不能编译IP,只能重新安装Quartus II 12.0sp2。同时,也安装了Nios II IDE 12.0sp2,Modelsim 10.c等软件。

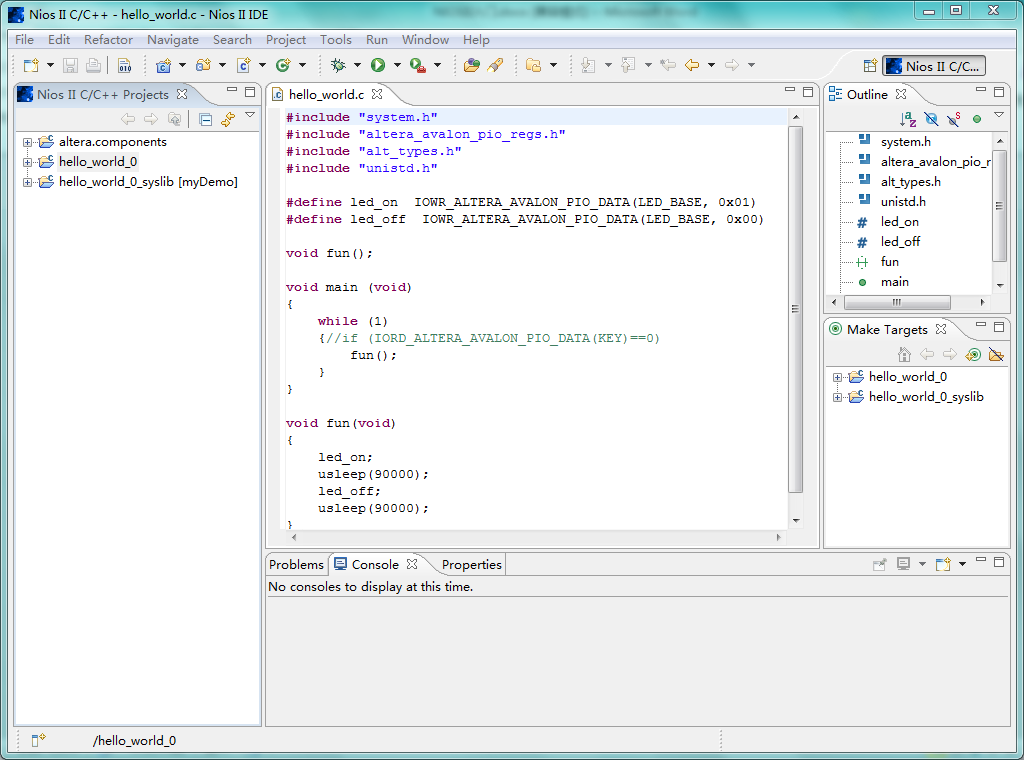

参考网上的Nios II实例,做了第一个实验:LED闪烁。

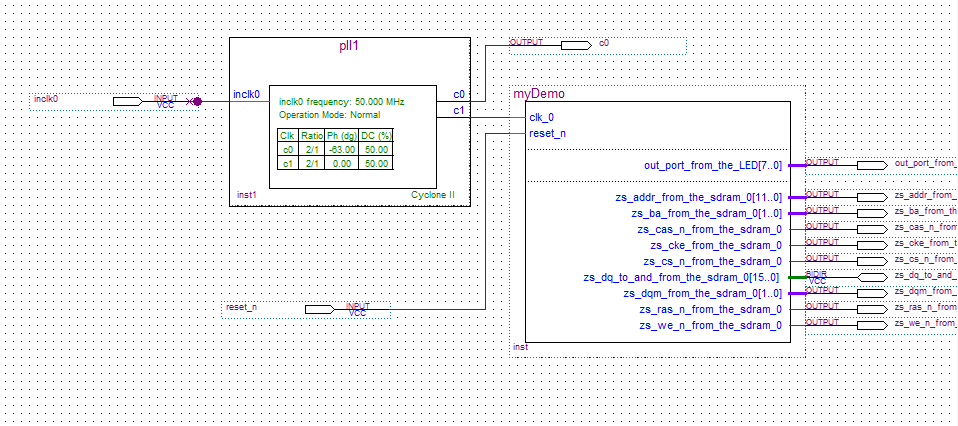

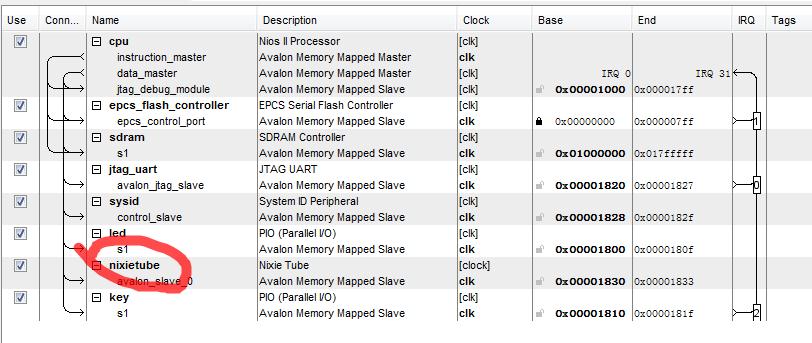

在Nios中构建的cpu、jtag_uart、sdram、led

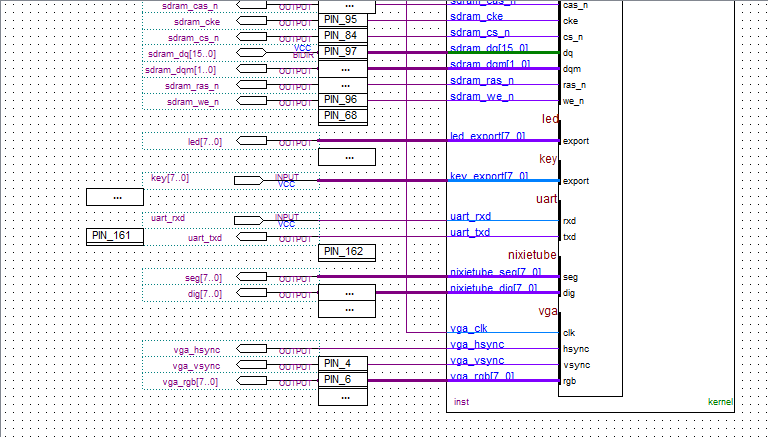

设计的原理图文件

第一个hello world程序,led闪烁

实验成功

10.12

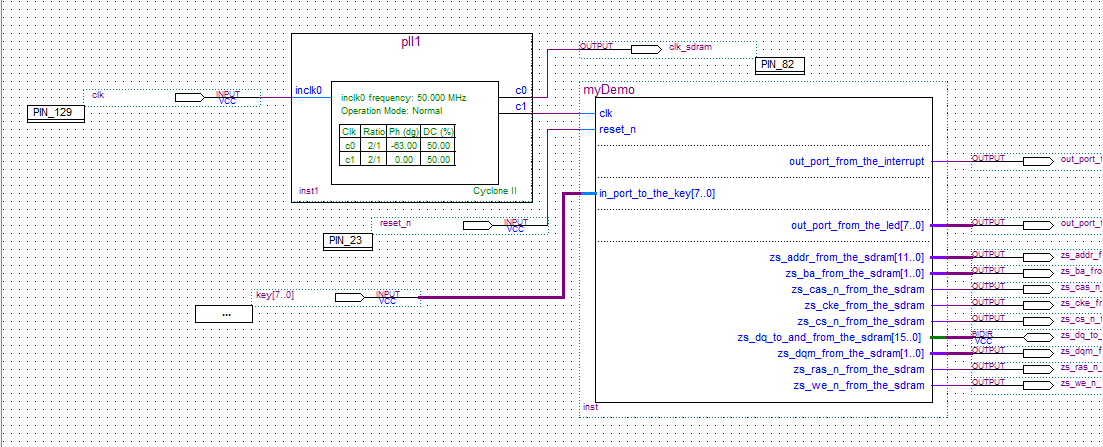

继续学习Nios II,进行key中断实验,遇到些问题,需要深入研究。

代码:

#include "system.h"

#include "altera_avalon_pio_regs.h"

#include "alt_types.h"

#include "sys/alt_irq.h"

#include "sys/alt_alarm.h"

#include "unistd.h"

#define led *(volatile unsigned char *) LED_BASE

#define key *(volatile unsigned char *) KEY_BASE

void Key_ISR(void* context, alt_u32 id);

void Key_Init();

//alt_u8 data;

//按键中断服务函数

void Key_ISR(void* context, alt_u32 id)

{

led = key;

while(key != 0xff);

IOWR_ALTERA_AVALON_PIO_EDGE_CAP(KEY_BASE, 0x00); //清中断捕获寄存器

}

//按键中断初始化

void Key_Init()

{

alt_irq_register(KEY_IRQ, 0, Key_ISR); //注册中断函数

IOWR_ALTERA_AVALON_PIO_IRQ_MASK(KEY_BASE, 0xff); //开KEY中断

IOWR_ALTERA_AVALON_PIO_EDGE_CAP(KEY_BASE, 0x00); //清中断捕获寄存器

}

int main(void)

{

Key_Init();

led = 0x55;

while(1);

return 0;

}

效果:按键中断,点亮对应的led

视频:http://v.qq.com/boke/page/b/4/q/b0106bte24q.html

10.20

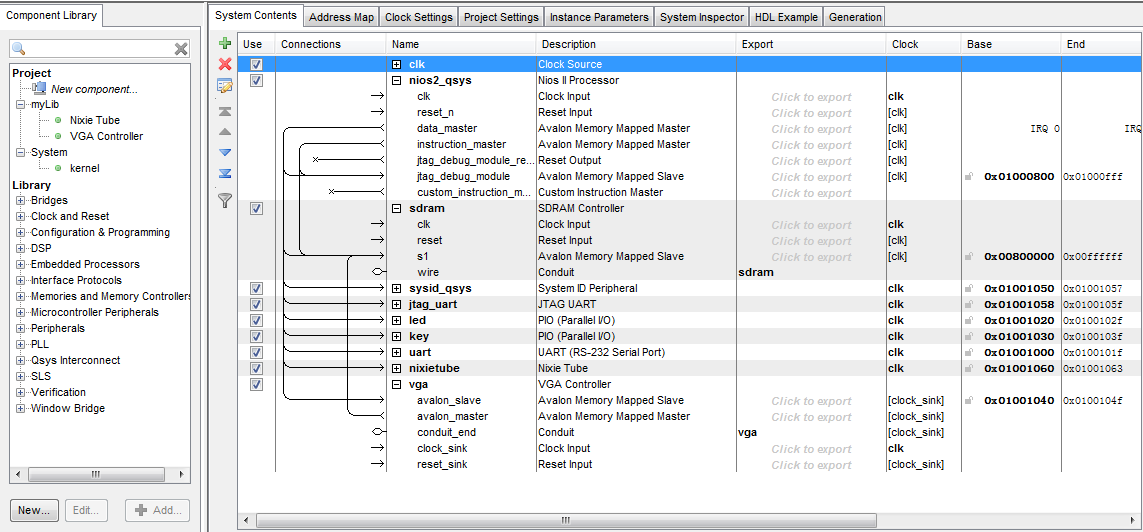

继续学习Nios II。需要设计自己的IP,研究了些资料,先制作数码管的IP核。

修改之前seg.v的代码。思路是通过avalon总线发送32bits数据,每4bits代表一个数码管,可以显示0~F。8个数码管动态刷新。

代码:

// SEG数码管模块

module seg_ip(

input clk, // 系统时钟输入,50MHz

input reset_n, // 系统复位输入

input write,

input [31:0]writedata,

output[7:0] seg, // seg输出

output[7:0] dig // dig输出

);

reg[6:0] seg_r;

reg[7:0] dig_r;

assign seg = { 1'b1, seg_r };

assign dig = dig_r;

reg[15:0] scan; //扫描

reg[31:0] seg_data;

//扫描时钟

always @(posedge clk or negedge reset_n)

begin

if(!reset_n)

scan = 16'd0;

else

scan = scan + 1'b1;

end

always @(posedge clk or negedge reset_n)

begin

if(!reset_n)

seg_data[31:0] <= 31'd0;

else if(write)

seg_data[31:0] <= writedata[31:0];

end

//片选

always @(scan[15:13])

begin

case(scan[15:13])

3'd0: begin dig_r <= ~8'h01; seg_r <= trans(seg_data[3:0]); end

3'd1: begin dig_r <= ~8'h02; seg_r <= trans(seg_data[7:4]); end

3'd2: begin dig_r <= ~8'h04; seg_r <= trans(seg_data[11:8]); end

3'd3: begin dig_r <= ~8'h08; seg_r <= trans(seg_data[15:12]); end

3'd4: begin dig_r <= ~8'h10; seg_r <= trans(seg_data[19:16]); end

3'd5: begin dig_r <= ~8'h20; seg_r <= trans(seg_data[23:20]); end

3'd6: begin dig_r <= ~8'h40; seg_r <= trans(seg_data[27:24]); end

3'd7: begin dig_r <= ~8'h80; seg_r <= trans(seg_data[31:28]); end

endcase

end

//译码任务

function [6:0] trans;

input [3:0] in_data;

begin

case(in_data[3:0])

0: trans = 7'b100_0000; // 0

1: trans = 7'b111_1001; // 1

2: trans = 7'b010_0100; // 2

3: trans = 7'b011_0000; // 3

4: trans = 7'b001_1001; // 4

5: trans = 7'b001_0010; // 5

6: trans = 7'b000_0010; // 6

7: trans = 7'b101_1000; // 7

8: trans = 7'b000_0000; // 8

9: trans = 7'b001_1000; // 9

10: trans = 7'b000_1000; // A

11: trans = 7'b000_0011; // b

12: trans = 7'b100_0110; // c

13: trans = 7'b010_0001; // d

14: trans = 7'b000_0110; // E

15: trans = 7'b000_1110; // F

default: trans = 7'b111_1111;

endcase

end

endfunction

endmodule

在IDE端,测试程序修改为:

#define seg *(volatile unsigned int *) NIXIETUBE_BASE

seg = data++;

按键一次,数据+1

继续学习NIOS II。

在调试uart出现一连串问题。把自带RS232的IP添加进去后,发现串口通信收发数据异常,参考网上实验教程,发现是打开了NIOS CPU的cache。重新完成后,发现uart果然正常收发数据了,但是led和key却没有反应了?!奇怪。显然,是打开cache引起的。上网查询,果然如此。打开cache,就不能直接对地址操作了,类似led=0xaa;就不行了。

LED=0x0; // 使PIO LED输出为0,此种方法在有数据CACHE时会失效

IOWR_ALTERA_AVALON_PIO_DATA(LED_BASE,0x0); // 使PIO LED输出为0

或者IOWR(LED_BASE,0,0); // 使PIO LED输出为0

这样修改完成后,一切恢复正常。

今天继续调试,又出现了新问题。在执行NIOS程序代码时,不能下载了:

Pausing target processor: not responding.

Resetting and trying again: FAILED

downloading ELF process failed

从网上查询知道,是sdram时钟与cpu时钟之间的问题,不过建议的方法一一试验过,均不起作用。最后,感觉是电路上可能出现问题。重新把引脚焊接一遍后,故障解除。

10.27

继续学习NIOS II。

参考网上资料,设计VGA的控制器IP。代码和之前的VGA实验代码差不多,增加了与SDRAM的读取方式。在SDRAM开辟一段显示缓存区域。VGA的分辨率为800x600,在50MHz时钟下,刷新频率为72Hz。

// VESA Signal 800x600 @ 72Hz timing

// Screen refresh rate: 72Hz

// Vertical refresh: 48.076923076923kHz

// Pixel freq.: 50.0MHz

// Horizontal timing (line)

parameter H_SYNC_PULSE = 120; // 行同步

parameter H_BACK_PORCH = 64; // 行同步后

parameter H_VISIBLE_AREA = 800; // 行图像显示

parameter H_FRONT_PORCH = 56; // 行同步前

parameter H_WHOLE_LINE = 1040; // 行总和

// Vertical timing (frame)

parameter V_SYNC_PULSE = 6; // 场同步

parameter V_BACK_PORCH = 23; // 场同步后

parameter V_VISIBLE_AREA = 600; // 场图像显示

parameter V_FRONT_PORCH = 37; // 场同步前

parameter V_TOTAL_FRAME = 666; // 场总和

在NIOS的测试程序,将屏幕分成32x8的小块,分别显示256色(1个字节)

#define VGA_WIDTH 800

#define VGA_HEIGHT 600

#define VGA_BUFFER_SIZE VGA_WIDTH*VGA_HEIGHT

#define VGA_SET_PIXEL(x,y,color) IOWR_8DIRECT((unsigned long)vga_buffer,(y*VGA_WIDTH)+x,color)

unsigned char vga_buffer[VGA_BUFFER_SIZE];

for(y = 0; y < VGA_HEIGHT; y++)

{

yy = y / 75;

for(x = 0; x < VGA_WIDTH; x++)

{

xx = x / 25;

color = yy * 32 + xx;

VGA_SET_PIXEL(x, y, color);

}

}

效果:

回复

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 基于ArduinoUNO开发板的AT24C02读写测试被打赏¥16元 | |

| TCS3472S传感器及其色彩检测被打赏¥19元 | |

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |