mmqm的进程贴

申请和下单已经实施完成,PCB、元器件和下载工具还未到达,先做些准备工作。

从活动主页下载开发板的原理图

http://www.eepw.com.cn/event/action/FPGA_DIY/tech.html

从核心板图看,FPGA是选择了EP2C8Q208C8,配置芯片是EPCS4SI8N。工作电源是3.3V和1.2V。提供JTAG和ASP接口。

从接口板图看,涉及以下实验:8个LED,8个Key,蜂鸣器,VGA,红绿黄LED,8位开关,PS2键盘和鼠标,RS232,液晶模块1602和12864,SD卡,ADC,DAC,温度,E2PROM,时钟,8个数码管,3个扩展接口

EP2C8Q208C8是属于Cyclone II系列,到altera官网研究了下,使用免费的开发工具软件就可以了,Quartus II网络版:

https://www.altera.com/download/software/quartus-ii-we/zh_cn

其他可能用到的软件以后用到再说

正式版和免费版的区别:

http://www.altera.com.cn/products/software/quartus-ii/compare-quartus-editions.pdf

Cyclone II器件资料

http://www.altera.com.cn/literature/lit-cyc2.jsp

实验板上用到的其他芯片都比较常见,资料都有

关键词: 进程

10.2

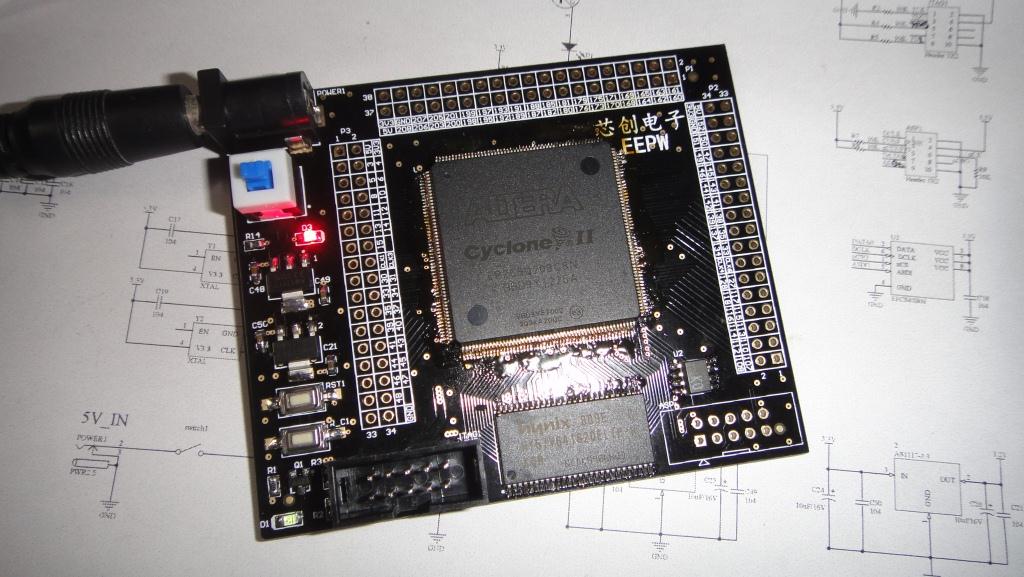

核心板上的FPGA芯片焊接是最难的工作,一定要仔细小心,如果是新手,建议找人代焊。对于北方干燥气候,还要特别注意防静电。

今日把核心板部分基本焊接完成。需要留意的就是有极性元件的安放,比如稳压二极管、发光二级管、钽电容。

用万用表检测是否有短路现象,然后上电。

目前核心板上只焊接了JTAG接口。

然后连接USB Blaster,驱动程序定位:

C:\altera\12.0sp2\quartus\drivers\usb-blaster

再打开Quartus II软件,确认下载线正确安装。

能够识别FPGA芯片,一切正常。实际使用的芯片是EP2C5Q208C8N。

为了完整测试,继续焊接接口板部分电路,包括LED和数码管。

编写一段流水灯程序,下载,工作正常。

视频:

http://v.qq.com/play/u0105pgpkoj.html

代码(Verilog HDL):

module demo(

clk,

rst,

led

);

input clk; //系统时钟输入,50MHz,0.02us

input rst; //系统复位输入

output [7:0] led; //led输出

reg [7:0] led;

reg clk1s; //分频时钟

reg [25:0] clk_cnt; //分频计数器

//系统时钟分频,产生1s的时钟

always @(posedge clk)

begin

if(clk_cnt == 25'd25000000)

begin

clk1s = ~clk1s;

clk_cnt = 0;

end

else

begin

clk_cnt = clk_cnt + 1'b1;

end

end

//流水灯

always @(posedge clk1s or negedge rst)

begin

if(rst == 0)

begin

led <= 8'b11111110;

end

else

begin

if(led == 8'b01111111) led <= 8'b11111110;

else led <= ~(~led << 1);

end

end

endmodule

10.4

空里找闲,继续实验了VGA功能。

电路很简单,就是几个电阻。关于VGA的知识上网学习了下。

参考:

http://www.tinyvga.com/vga-timing/800x600@72Hz

http://bbs.****.com/BLOG_ARTICLE_184836.HTM

实验内容:

显示800x600分辨率,72Hz刷新,时钟50MHz。用示波器测试,都符合。

屏幕分成8x6块,每块100x100。RGB三色中红色用行计数,绿色用场计数,蓝色是1s变化一次

视频:

http://v.qq.com/boke/page/f/o/v/f0105udngov.html

代码:

//VGA模块

//VESA 800x600@72Hz(pixel clock 50.0MHz)

module m_vga(clk, rst, hsync, vsync, vga_r, vga_g, vga_b);

input clk; //系统时钟输入,50MHz,0.02us

input rst; //系统复位输入

output hsync; //行同步输出,48kHz

output vsync; //场同步输出,72Hz

reg hsync, vsync;

output[2:0] vga_r; //RGB信号输出

output[2:0] vga_g;

output[1:0] vga_b;

reg[10:0] pixel; //行向时序,1040像素

reg[9:0] line; //场向时序,666行

//行向时序

always @(posedge clk or negedge rst)

begin

if(rst == 0) pixel <= 11'd0;

else if(pixel == 11'd1040) pixel <= 11'd0;

else pixel <= pixel + 1'b1;

end

//场向时序

always @(posedge clk or negedge rst)

begin

if(rst == 0) line <= 10'd0;

else if(line == 10'd666) line <= 10'd0;

else if(pixel == 11'd1040) line <= line + 1'b1;

end

//hsync信号(行同步),vsync信号(场同步)

always @(posedge clk or negedge rst)

begin

if (rst == 0)

begin

hsync <= 1'b0;

vsync <= 1'b0;

end

else

begin

hsync <= pixel >= 11'd120;

vsync <= line >= 10'd6;

end

end

reg[2:0] xpos;

reg[2:0] ypos;

parameter

Left = 120 + 64,

PixelWidth = 100,

Top = 6 + 23;

//计算8x6色块行地址

always @(posedge clk or negedge rst)

begin

if(rst == 0) xpos <= 3'b000;

else if(pixel >= Left && pixel < Left + PixelWidth) xpos <= 3'b000;

else if(pixel >= Left + PixelWidth && pixel < Left + 2 * PixelWidth) xpos <= 3'b001;

else if(pixel >= Left + 2 * PixelWidth && pixel < Left + 3 * PixelWidth) xpos <= 3'b010;

else if(pixel >= Left + 3 * PixelWidth && pixel < Left + 4 * PixelWidth) xpos <= 3'b011;

else if(pixel >= Left + 4 * PixelWidth && pixel < Left + 5 * PixelWidth) xpos <= 3'b100;

else if(pixel >= Left + 5 * PixelWidth && pixel < Left + 6 * PixelWidth) xpos <= 3'b101;

else if(pixel >= Left + 6 * PixelWidth && pixel < Left + 7 * PixelWidth) xpos <= 3'b110;

else if(pixel >= Left + 7 * PixelWidth && pixel < Left + 8 * PixelWidth) xpos <= 3'b111;

else xpos <= 3'b000;

end

//计算8x6色块场地址

always @(posedge clk or negedge rst)

begin

if(rst == 0) ypos <= 3'b000;

else if(line >= Top && line < Top + PixelWidth) ypos <= 3'b000;

else if(line >= Top + PixelWidth && line < Top + 2 * PixelWidth) ypos <= 3'b001;

else if(line >= Top + 2 * PixelWidth && line < Top + 3 * PixelWidth) ypos <= 3'b010;

else if(line >= Top + 3 * PixelWidth && line < Top + 4 * PixelWidth) ypos <= 3'b011;

else if(line >= Top + 4 * PixelWidth && line < Top + 5 * PixelWidth) ypos <= 3'b100;

else if(line >= Top + 5 * PixelWidth && line < Top + 6 * PixelWidth) ypos <= 3'b101;

else ypos <= 3'b110;

end

reg clk1s; //分频时钟

reg[25:0] clk_cnt; //分频计数器

//系统时钟分频,产生1s的时钟

always @(posedge clk)

begin

if(clk_cnt == 25'd25000000)

begin

clk1s = ~clk1s;

clk_cnt = 0;

end

else

begin

clk_cnt = clk_cnt + 1'b1;

end

end

reg[1:0] color_cnt;

//每1s改变蓝色

always @(posedge clk1s or negedge rst)

begin

if(rst == 0)

color_cnt = 2'b00;

else

color_cnt <= color_cnt + 1'b1;

end

wire[7:0] color;

reg [7:0] color_r;

always @(posedge clk or negedge rst)

begin

if(rst == 0)

begin

color_r = 8'b00000000;

end

else

begin

color_r <= { xpos, ypos, color_cnt }; //红色+绿色+蓝色

end

end

assign color = color_r;

//显示区标志

wire valid;

assign valid = (pixel > 10'd184) && (pixel < 10'd984) && (line > 10'd29) && (line < 10'd629);

//颜色输出

assign vga_r[2] = valid ? color[7] : 1'b0;

assign vga_r[1] = valid ? color[6] : 1'b0;

assign vga_r[0] = valid ? color[5] : 1'b0;

assign vga_g[2] = valid ? color[4] : 1'b0;

assign vga_g[1] = valid ? color[3] : 1'b0;

assign vga_g[0] = valid ? color[2] : 1'b0;

assign vga_b[1] = valid ? color[1] : 1'b0;

assign vga_b[0] = valid ? color[0] : 1'b0;

endmodule

SEG数码管动态显示,采用扫描方式,轮询,只要满足刷新频率快于人眼视觉暂留时间即可。

程序比较简单,1s间隔分别显示0~7,8~F

代码:

//SEG数码管模块

module m_seg(clk, rst, seg, dig);

input clk; //系统时钟输入,50MHz

input rst; //系统复位输入

output[7:0] seg; //seg输出

output[7:0] dig; //dig输出

reg[6:0] seg_r;

reg[7:0] dig;

assign seg = { 1'b1, seg_r };

reg[15:0] scan; //扫描

//扫描时钟

always @(posedge clk or negedge rst)

begin

if(rst == 0)

scan = 16'd0;

else

scan = scan + 1'b1;

end

//片选

always @(scan[15:13])

begin

case(scan[15:13])

3'd0: dig <= ~8'h01;

3'd1: dig <= ~8'h02;

3'd2: dig <= ~8'h04;

3'd3: dig <= ~8'h08;

3'd4: dig <= ~8'h10;

3'd5: dig <= ~8'h20;

3'd6: dig <= ~8'h40;

3'd7: dig <= ~8'h80;

endcase

end

//译码

always @(scan[15:13] or n)

begin

case(scan[15:13] + n)

0: seg_r <= 7'b100_0000; // 0

1: seg_r <= 7'b111_1001; // 1

2: seg_r <= 7'b010_0100; // 2

3: seg_r <= 7'b011_0000; // 3

4: seg_r <= 7'b001_1001; // 4

5: seg_r <= 7'b001_0010; // 5

6: seg_r <= 7'b000_0010; // 6

7: seg_r <= 7'b101_1000; // 7

8: seg_r <= 7'b000_0000; // 8

9: seg_r <= 7'b001_1000; // 9

10: seg_r <= 7'b000_1000; // A

11: seg_r <= 7'b000_0011; // b

12: seg_r <= 7'b100_0110; // c

13: seg_r <= 7'b010_0001; // d

14: seg_r <= 7'b000_0110; // E

15: seg_r <= 7'b000_1110; // F

default: seg_r <= 7'b111_1111;

endcase

end

reg clk_1s; //分频时钟

reg [25:0] clk_cnt; //分频计数器

//系统时钟分频,产生1s的时钟

always @(posedge clk)

begin

if(clk_cnt == 25'd25000000)

begin

clk_1s = ~clk_1s;

clk_cnt = 25'd0;

end

else

begin

clk_cnt = clk_cnt + 1'b1;

end

end

reg[3:0] n;

always @(posedge clk_1s or negedge rst)

begin

if(rst == 0)

n <= 4'd0;

else

n <= n + 4'd8;

end

endmodule

测试按键功能,主要是去抖动问题。

软件一般按键抖动通过延时10~20ms判断,硬件一般用RS触发器电路。

实际应用中,按键功能比较复杂,比如长按、短按、多键等。

这里简化处理,测试去抖时间为100ms,因此如果在100ms内按下又弹起,就认为按键无效;按下超过100ms,就有效。最终应用可以修改成20ms。

同时按下多键也能识别。

视频:

http://v.qq.com/boke/page/i/2/c/i0105jszk2c.html

代码:

//KEY模块

module m_key(clk, rst, key, led);

input clk; //系统时钟输入,50MHz,0.02us

input rst; //系统复位输入

input[7:0] key;

output[7:0] led; //led输出

reg[7:0] led;

reg key_down;

reg[7:0] key_reg;

reg[22:0] key_cnt;

always @(posedge clk or negedge rst)

begin

if(!rst)

begin

key_down <= 1'b1;

key_reg <= 8'hff;

key_cnt <= 23'd0;

end

else if(key != key_reg)

begin

key_reg <= key;

key_cnt <= 23'd0;

end

else

begin

if(key_cnt == 23'd5000000) //5000000*0.02us=100ms

key_down <= key_reg == 8'hff;

else

key_cnt <= key_cnt + 1'b1;

end

end

always @(negedge key_down)

begin

if(led == key_reg)

led <= 8'hff;

else

led <= key_reg;

end

endmodule

LZ,你的视频不想在这里出现下?

http://v.eepw.com.cn/video/list/company/Altera

回复

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 基于ArduinoUNO开发板的AT24C02读写测试被打赏¥16元 | |

| TCS3472S传感器及其色彩检测被打赏¥19元 | |

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |