各位大侠,我的晶振好像没有起振,写了几个程序测试了一下,口没有反应,我接到的二个晶振上,即Y2,谁能发一个确定通过测试的SOF文件给我测试一下啊

啸风(1642713730) 12:37:59

群 里有共享

EEPW-caipengxiang<caiawf293337@qq.com> 12:39:09

是接在那个晶振上?

啸风(1642713730) 12:40:06

y1吧

啸风(1642713730) 12:41:00

我改下 y2

下面是sof文件

smg_8bit.rar

我的只显示零,没有变

日月潭离开氟 12:48:35

这是不是说明我的晶振没有焊接好或是坏了?

海贼wang_XCG 12:49:22

你重新焊一下 看看

海贼wang_XCG 12:49:45

用两个烙铁 把它卸下来

日月潭离开氟 12:50:13

主要是那个晶振旁边有一排插针在,卸不了

海贼wang_XCG 12:50:35

可以卸 我卸过

海贼wang_XCG 12:51:33

两个烙铁一起工作

日月潭离开氟 12:51:58

好,我去试试,谢谢

海贼wang_XCG 12:52:02

还有松香一起

海贼wang_XCG 12:52:19

将四个焊盘预热

海贼wang_XCG 12:52:35

很轻松就卸下来了

日月潭离开氟 12:52:54

预热?

海贼wang_XCG 12:53:20

就是使锡融化

日月潭离开氟 12:53:52

哦,

非常的感谢,跑起来了,果然是没有焊接好,

提问者:caipengxiang

回答者:啸风

今天下午做了一下1602液晶显示,发现了一个1602的第三管脚接的R59的阻值太小以至于在显示字符时看不清,原因是对比度不够。

解决的办法:

将R59这个1k的电阻卸下,换上一个10K的电阻,显示就非常的清晰了。

2、液晶显示

此液晶显示内容是:在第一行显示EEPW 并附加一个数字在不停地从0~9变化,第二行显示本人的用户名caipengxiang;

下面附上sof文件

——回复可见内容——

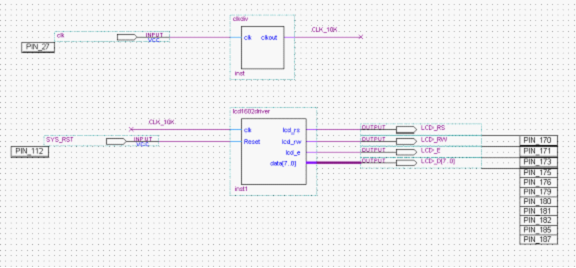

由于工程包含了好几个文件,就不附加代码了,贴一个原理图吧

截图有点不清楚,请见谅啊。

注:我使用的晶振是Y2

由于照相机拍照时液晶里面的内容显示不出来,有兴趣的可以下载sof文件自己测试一下

动态数码管显示,将Y2的50M频率经分频后动态扫描数码管显示。

注意:如果不进行分频的话,由于频率太高,数码管将不会显示任何数字。

下面是给出了分频器和动态扫描代码及SOF文件:(晶振使用Y2)

——回复可见内容——

LED灯闪烁

LED闪烁:

library ieee;

use ieee.std_logic_1164.all;

entity led is

port(clk: in std_logic;

ledout:out std_logic_vector(7 downto 0));

end entity;

architecture behave of led is

signal cnt: std_logic;

begin

process(clk)

begin

if clk'event and clk='1' then

cnt<=not cnt;

case cnt is

when '0'=>

ledout<="00000000";

when '1'=>

ledout<="11111111";

end case;

end if;

end process;

end behave;

分频:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity clkdiv is

port(clk : in std_logic;

clkout : out std_logic);

end clkdiv;

architecture behave of clkdiv is

signal cnt : std_logic_vector(35 downto 0);

begin

process(clk)

begin

if clk'event and clk = '1' then

if cnt > 19999999 then

cnt <= (others => '0');

clkout <= '0';

elsif cnt > 9999999 then

clkout <= '1';

cnt <= cnt + 1;

else

cnt <= cnt + 1;

end if;

end if;

end process;

end behave;

首先提出我发现的一个问题:

在做拨码开关时,程序写好了,编译,没有错误,但在分配管脚时使用108管脚时出错了,原因是108管脚时复用功能引脚,错误提示是:

Error:

Can't place multiple pins assigned to pin location Pin_108 (IOC_X28_Y2_N0)

Info: Pin b[1] is assigned to pin location Pin_108 (IOC_X28_Y2_N0)

Info: Pin ~LVDS41p/nCEO~ is assigned to pin location Pin_108 (IOC_X28_Y2_N0)

由于上述原因,拨码开关的第二个管脚就没有使用到108脚,在分配管脚时不使用108管脚编译就没有错误了。具体怎样解决这个问题,我还不清楚,还得那位大虾指教一下。

此问题已有大侠解决:

http://forum.eepw.com.cn/thread/221279/1

拨码开关控制LED亮灭VHDL代码:

library ieee;

use ieee.std_logic_1164.all;

entity boma is

port(b:in std_logic_vector(7 downto 0);

d: out std_logic_vector(7 downto 0));

end entity ;

architecture behave of boma is

begin

process(b)

begin

d<=b;

end process;

end behave;

好简单的一个程序

回复

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |

| 【S32K3XX】LIN 通讯模块使用被打赏¥31元 | |

| 【FreeRtos】FreeRtos + MPU模块的配置使用被打赏¥32元 | |

不错啊,问题解决了

不错啊,问题解决了