3:完成按键作业:

忙着做项目,所以只能闲暇时做做DIY的作业,只是想有些自己的收获,所以慢慢更新,活动的日期就不关心了!关键是能学到东西!

利用去抖动按键切换数码管,显示0~9.

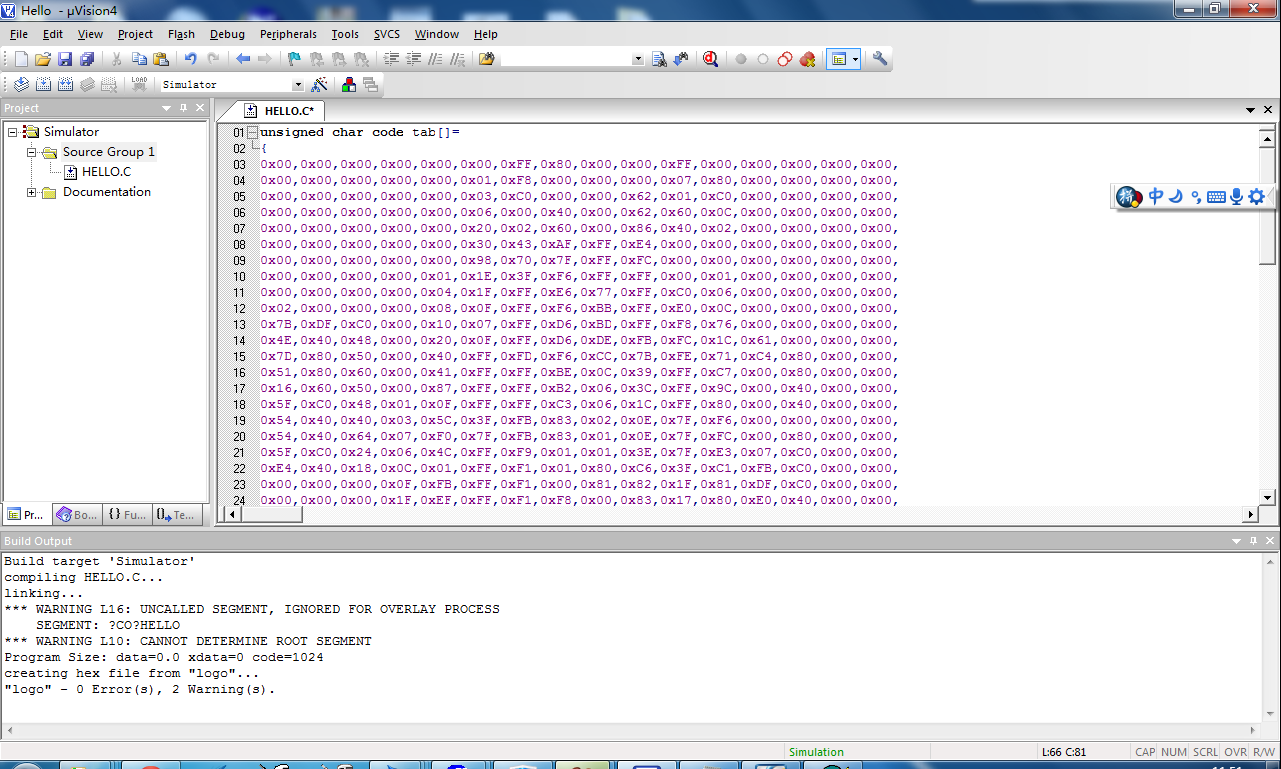

程序:

module key_data(sys_clk,sys_rstn,key_in,sm_seg,sm_bit);

//输入信号

input sys_clk;//50Hz

input sys_rstn;

input key_in;

//输出信号

output [7:0] sm_seg; //段码

output [7:0] sm_bit; //位码

//寄存器

reg [7:0] sm_seg;

reg [7:0] sm_bit;

reg [15:0] cnt ;

reg [19:0] delay_cnt;

wire key_scan;

wire key_low;

reg key_samp;

reg key_samp_r;

reg key_rst;

reg key_rst_r;

/*************************

按键脉冲边沿检测

***************************/

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

key_samp<=1'b1;

else

key_samp<=key_in;

end

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

key_samp_r<=1'b1;

else

key_samp_r<=key_samp;

end

assign key_scan=key_samp_r&(~key_samp);

/*************************************

延迟20ms

************************************/

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

delay_cnt<=20'h0;

else if(key_scan)

delay_cnt<=20'h0;

else//按键按下

delay_cnt<=delay_cnt+1'b1;

end

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

key_rst<=1'b1;

else if(delay_cnt==20'hfffff)

key_rst<=key_in;

end

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

key_rst_r<=1'b1;

else

key_rst_r<=key_rst;

end

assign key_low=key_rst_r&(~key_rst);

/***********************************

***********************************/

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

cnt<=4'b0000;

else if(key_low)

begin

cnt<=cnt+1'b1;

if(cnt==4'b1001)

cnt<=4'b0000;

end

end

always@(posedge sys_clk or negedge sys_rstn)

begin

sm_bit<=8'b10101010;

case(cnt)

4'b0000:sm_seg<=8'hc0;

4'b0001:sm_seg<=8'hf9;

4'b0010:sm_seg<=8'ha4;

4'b0011:sm_seg<=8'hb0;

4'b0100:sm_seg<=8'h99;

4'b0101:sm_seg<=8'h92;

4'b0110:sm_seg<=8'h82;

4'b0111:sm_seg<=8'hf8;

4'b1000:sm_seg<=8'h80;

4'b1001:sm_seg<=8'h90;

default:sm_seg<=8'hc0;

endcase

end

endmodule

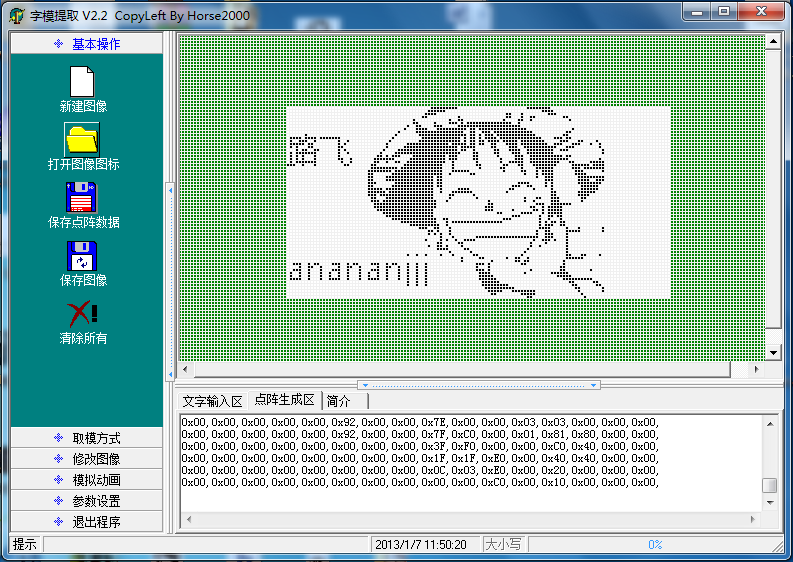

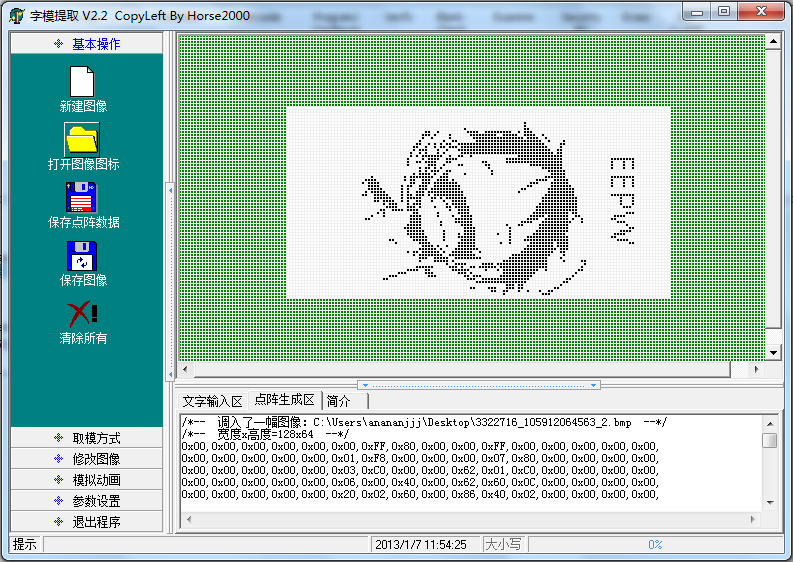

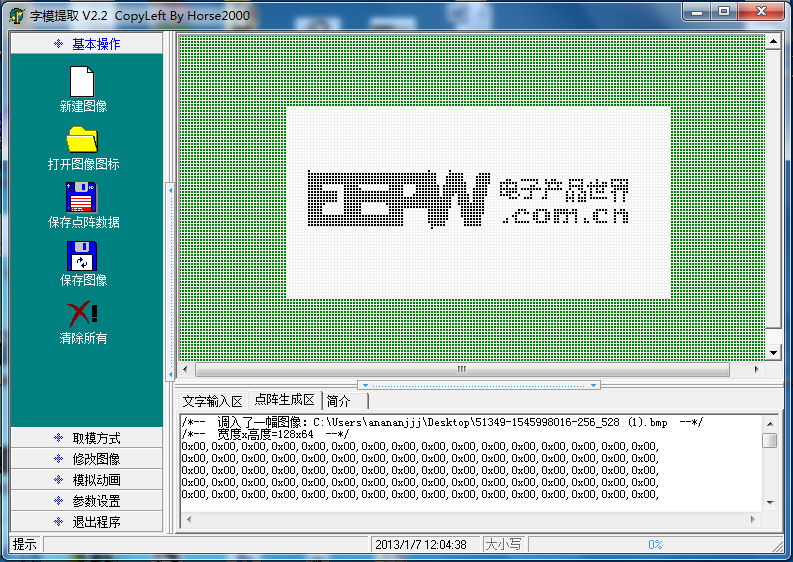

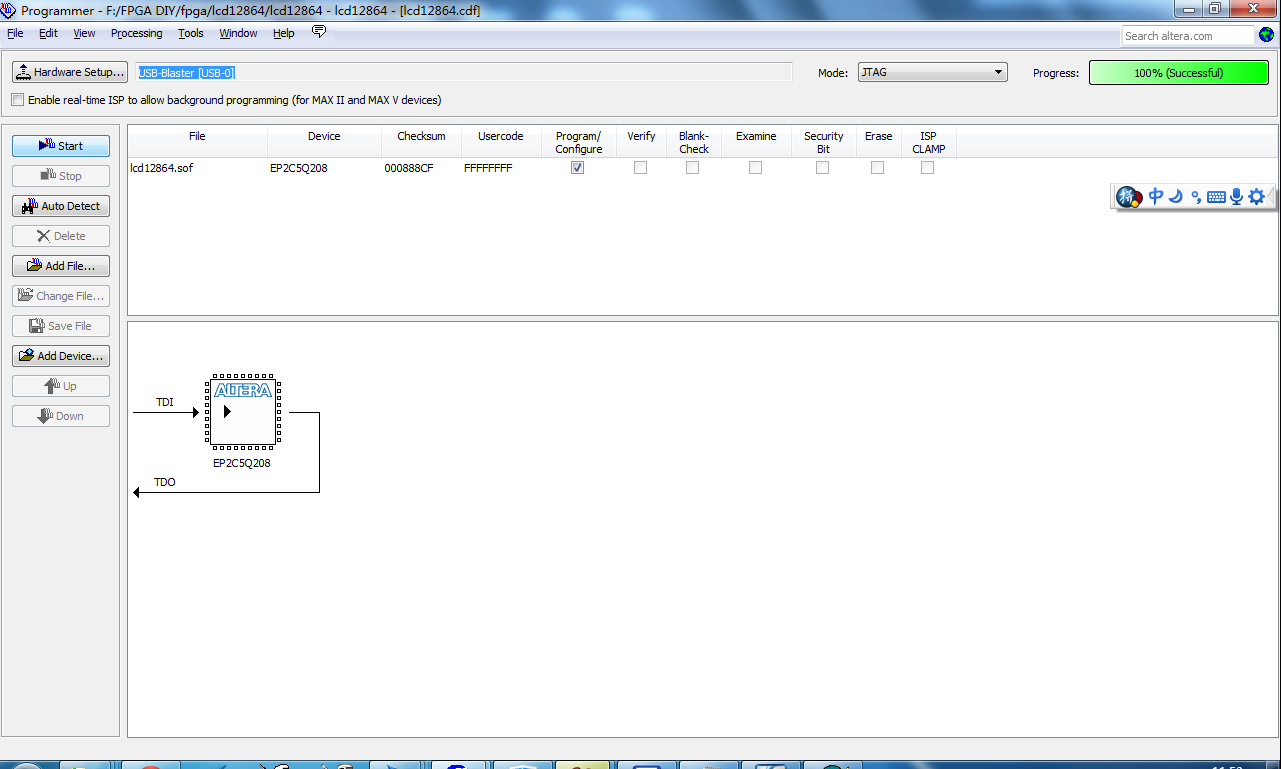

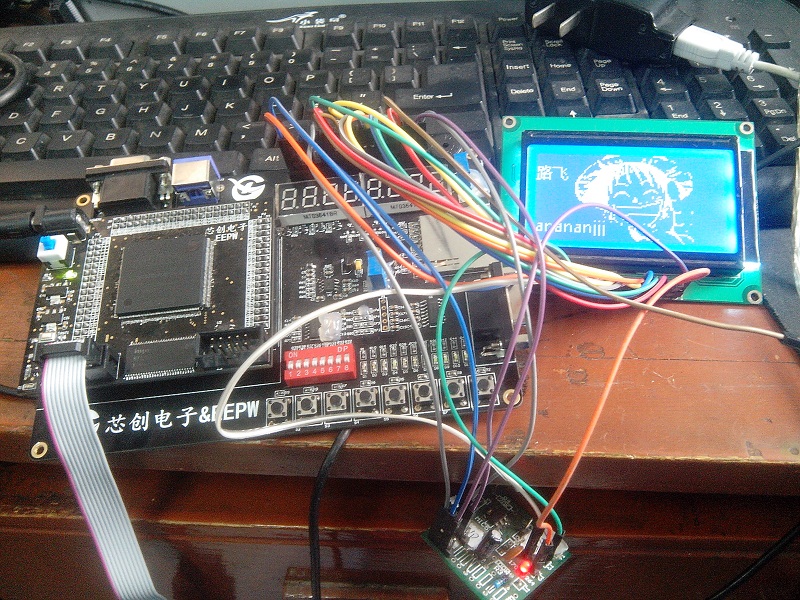

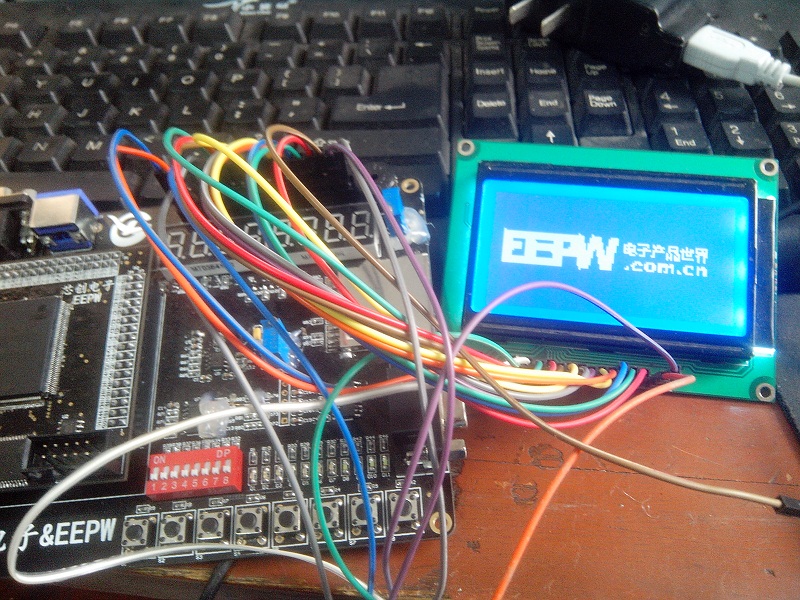

图片:

视频:

我要赚赏金

我要赚赏金