作者:武昌理工学院 周平 王平 付勇

指导教师:吴艳玲 邹熙

作品简介

平台选型说明

设计说明

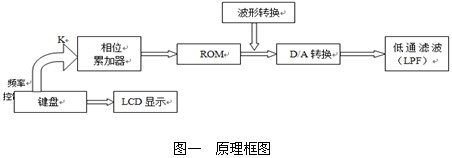

相位累加器:它由一个加法器和一个位相位寄存器组成,每来一个时钟,相位寄存器以步长增加,设计频率步进为10Hz,根据![]() ,得:

,得:![]() =10,因输出频率范围为10Hz~10kHz,则1 k 1000。由于基准频率

=10,因输出频率范围为10Hz~10kHz,则1 k 1000。由于基准频率![]() , 则有2N =

, 则有2N =![]() /10≈20000,取N=11,当K=1000时,在正弦波一个周期内基本上可以取16点,即可达到无失真。

/10≈20000,取N=11,当K=1000时,在正弦波一个周期内基本上可以取16点,即可达到无失真。

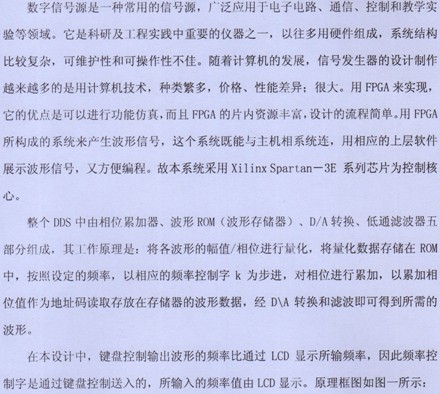

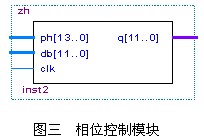

波形转换:ROM查询表中数字量化的波形为0~T/2的幅值为0~127的周期波,因此必须把相位累加器中的寄存器的内容波形变换,使之为正弦波。具体操作是:将T/2~T内波形的取反,并且将正弦波整体上移,使数字幅值范围为0~255。通过编程实现后生成元件如图三所示:

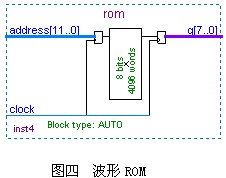

波形ROM:将相位累加器输出的数据作为波形存储器的取样地址,进行波形的相位/幅度转换,即可在给定时间上确定输出波形的抽样幅值。N位的寻址ROM相当于把0°~360°的正弦信号离散成具有 个样值序列,本设计波形ROM有14位数据位,即 个样值的幅度以14位二进制数值存在ROM中,所取的地址不同,输出对应正弦信号的幅度。

波形存储器(ROM)通过调用rom元件实现,其rom的值rom.mif是一个存放波形幅值的文件。

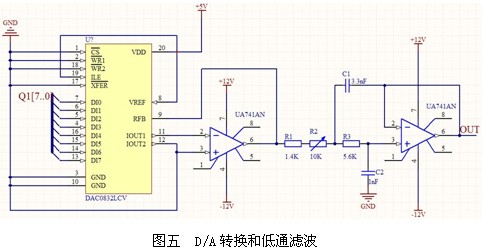

D/A转换:D/A转换是把正弦数字量转换成模拟量输出,合成的波形幅度量化序列经D/A转换成包络为正弦的阶梯波,其中D/A的分辨率越高,合成正弦波的台阶数越多,输出波形的精度越高。本实验采用DAC0832和OP07CP构成D\A转换模块,输出电压的P-P值为5V。

作品特色

本作品是基于FPGA的信号发生器,所产生的信号稳定,精度高,频率可以预置,系统结构比较简单,可维护性和可操作性良好,体积小便于携带,性价比高,功耗低,低碳环保。

系统演示视频:http://v.eepw.com.cn/video/play/id/2355

我要赚赏金

我要赚赏金