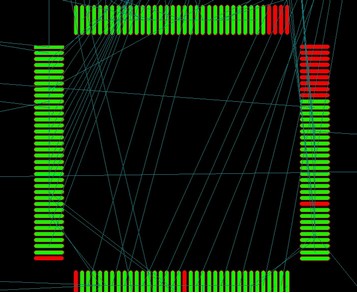

在将原理图导入到PCB之后为什么有部分的管脚变绿?其管脚间距都是一样的,为什么不是全部的变绿呢?

修改规则间距能将此问题解决,只是不解为什么会出现部分变绿的现象?望有知道的高手给予赐教,多谢

导入前你是没有对规则(rules)进行设置的,软件采用默认或者上一次的设置

由于你导入的元件封装或其他违反了设置的规则,才会出现绿色(绿色默认情况下是出错的标志)

你的封装是没有问题的,例如:默认规则不允许10mil以内的间距,而你恰好在这个元件的管脚间距的设计上设计成了8mil,就会出现这样的提示

一般情况下,如果确认只是规则错误而又看不惯这种提示你就先把他屏蔽掉

等你绘制完PCB后进行DRC检查时再来改这些错误