作业留几天,今天终于有空做了。

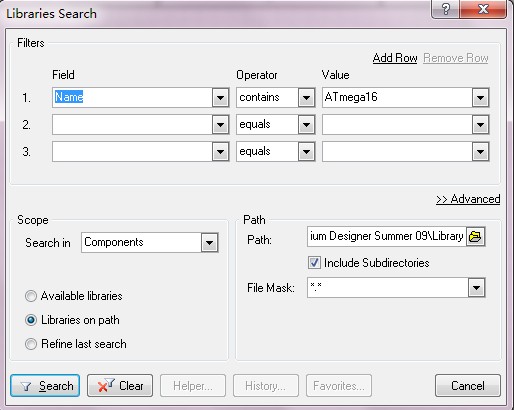

首先查找主控CPU:点击右侧Library

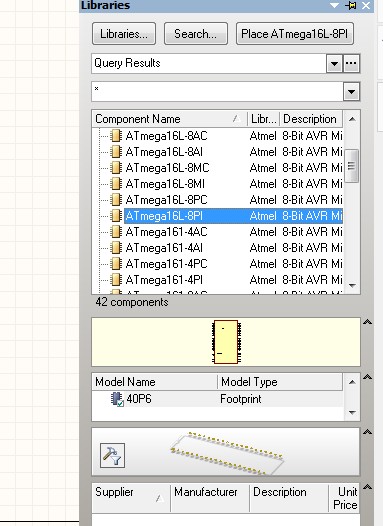

搜到的结果

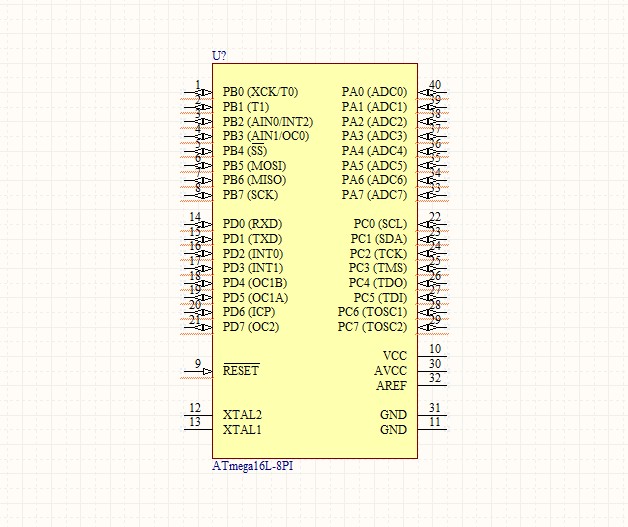

双击添加进原理图。如图:

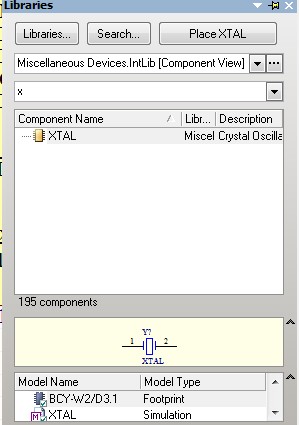

接着依次添加其他器件,常用器件一般都在Miscellaneous Devices中,如下图输入X自动搜索到晶振,类推,R代表电阻,C代表电容……

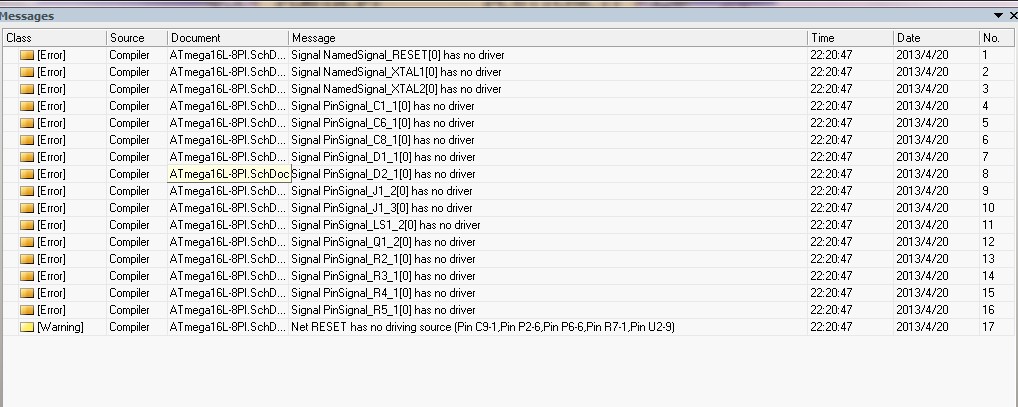

所有器件添加完毕,并且编号,编译出现下面的错误:

解决方法:

将schematic原理图添加到某工程,再编译就不会出现那些error了。

解法一:你使用的元件对应的引脚是输入的,可以改变原理图中对应元器件的引脚属性解决。 解法二:在protel中,软件会检查你的输入管脚有没有连,这样的好处是提醒画图的人还有输入管脚悬空的,我们知道,在电路系统中,大部分输入管脚是不允许悬空 的.所以建议画图的人在做原理图库的时候尽量把元件管脚的属性加上,这样可以不让自己出错.如果有输入哪个管脚必须悬空的话,可以在上面添加忽略ERC检查.这样编译的时候就没有警告了! 解发三:在做元件封装的时候,管脚的electrical type有很多选择,一般情况下,选择passive就没事了 解发四:设置属性。在Project-Error Reporting-Violations Associated with Nets

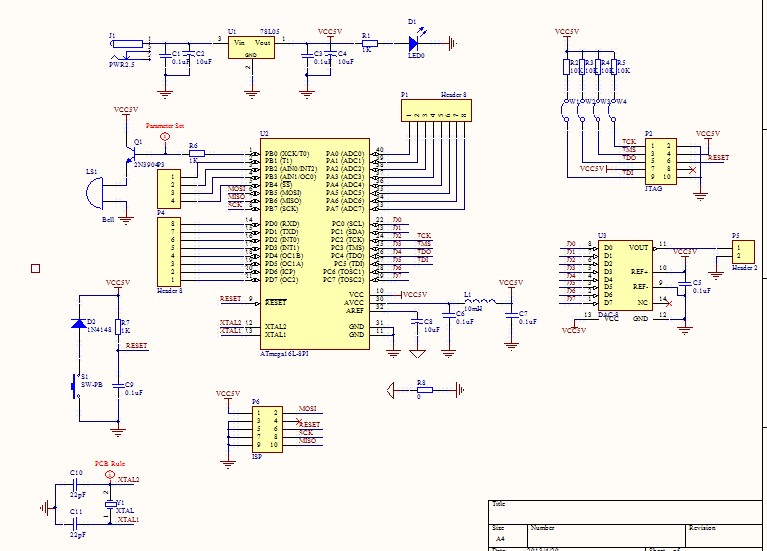

Signals with no driver中,选择no report. 总的原理图如下:

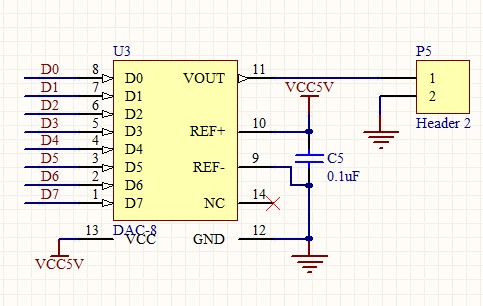

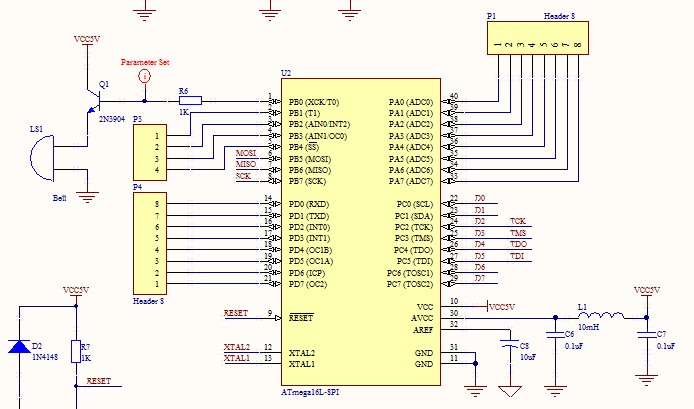

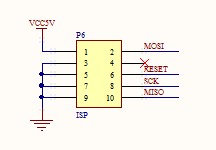

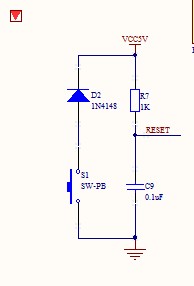

各部分原理图:

各部分原理图:

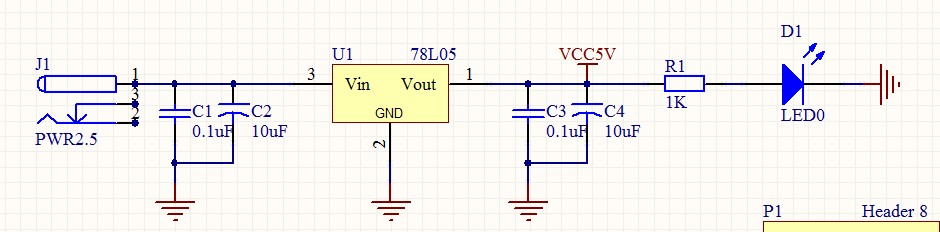

电源部分

电源部分

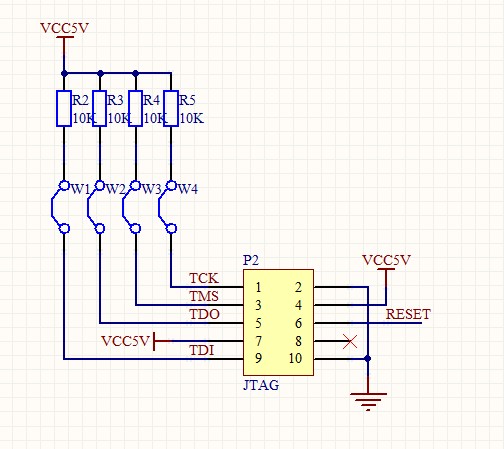

JTAG

JTAG

8位DAC

8位DAC

主控部分

ISP下载

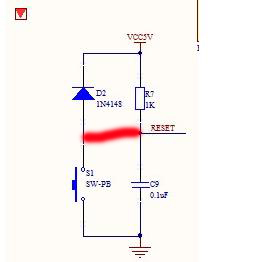

复位电路

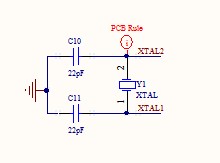

晶振

Ok,作业到此结束。

我要赚赏金

我要赚赏金