学习STM32也有一段时间了,并且着手画过几块STM32的实验板,这中间学到了不少的知识,在此做个小结,以便今后的查找一种,打算介绍一下最小系统设计过程中需要注意的事项,如供电、时钟管理、复位控制、启动模式的设置和调试管理等。

1、独立A/D转换器供电以及参考电压(有二)

A、一个独立的VDDA引脚给ADC供电

B、VSSA引脚提供一个隔离的接地输入

若有VREF–(取决于封装)时,它必须连到VSSA。

VREF+引脚可以连接到VDDA外部电源。如果在VREF+上使用单独的外部参考电压,必须在这个引脚上连接一个10nF和一个1μF的电容。在所有情况下,VREF+必须在2.4V和VDDA之间。

没有VREF+和VREF-,它们在内部分别被连接到ADC的供电电源(VDDA)和ADC的地(VSSA)。

2、备用电池

VBAT引脚必须被连接到外部电池(1.8V < VBAT < 3.6V)。如果没有外部电池,这个引脚必须和100nF的陶瓷电容一起连接到VDD电源上

3、时钟负载电容

负载电容C遵循以下公式:C = C21 x C24 / (C21 + C24) + Cstray。这里,Cstray是引脚电容以及PCB相关的电容。典型值在2pF到7pF 之间。

谐振器和负载电容需要尽可能近地靠近振荡器的引脚,以减小输出失真和启动稳定时间。负载电容值必须根据选定的晶振进行调节。

对于C21和C24通常具有相同的值。晶体制造商通常指定一个负载电容值,该值为C21和C24的并联电容值。当选择C21和C24时,PCB和MCU引脚的电容值也必须被计算进去(10pF可作为引脚和板电容的粗略估计)。

4、如果采用外部时钟源,如有源晶振

在这种模式下,必须提供一个外部时钟源。它的频率可高达25MHz。外部时钟信号(占空比为50%的方波、 正弦波或三角波)必须连到OSC_IN引脚,同时保证OSC_OUT引脚悬空。

5、关于调试端口

STM32F10x内核集成了串行线/JTAG调试接口。这是标准的ARM® CoreSight调试接口,包括JTAG – DP接口(5引脚)和SW – DP接口(2引脚)。

A、JTAG调试接口(JTAG – DP)为AHP – AP模块提供5针标准JTAG接口。

B、串行线调试接口(SW – DP)为AHP – AP模块提供2针(时钟+数据)接口。

在SWJ – DP接口中,SW – DP的2个引脚与JTAG 接口的5个引脚中的一些是复用的。在此一般选择5线制的10针JTAG,也可以扩展为20针的JTAG接口。

JTAG的IEEE标准推荐对TDI,TMS和nTRST上拉,但是对TCK没有特别建议。然而,在STM32F10xxx中JTCK引脚有下拉电阻。一般的应用中统统外接10K的上拉。

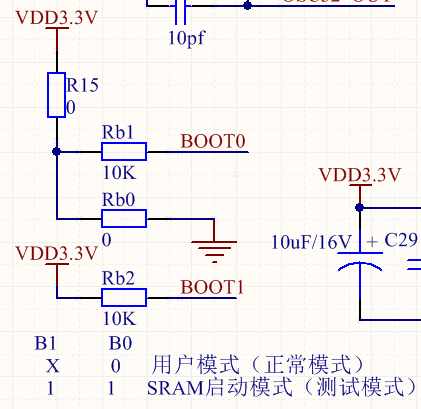

6、关于启动模式

7、去耦合

每个模块都应该单独接地,所有的地最终都应在一个点上连到一起。尽量避免或者减小回路的区域。为了减少供电回路的区域,电源应该尽量靠近地线,这是因为,供电回路就像个天线,成为EMI的发射器和接收器。

STM32上每个电源引脚以及用到的IC的电源端应该并联去耦合的滤波陶瓷电容C(100nF)和化学电容C(10μF)。这些电容应该尽可能的靠近电源/地引脚;典型值一般从10nF到100nF,具体的容值取决于实际应用的需要。

大致的就这些吧,后期在做添加,欢迎大家补充指点。

我要赚赏金

我要赚赏金