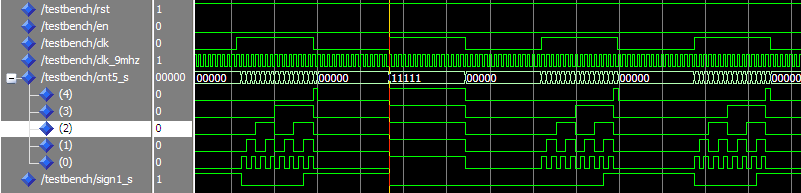

利用大频率时钟对小频率时钟采样,来判断大频率时钟的频率范围。计数器计数出错![]()

process(Clk_9MHz,Rst,En,Clk,Cnt5)

begin

if(Rst ='0') then

Sign1 <='1';

Cnt5 <= "00000";

elsif(Clk_9MHz'event and Clk_9MHz='1') then

--Clk_9MHz为大频率时钟,理论是9MHz,但实际需测试其频率范围

if(En='0') then --使能有效

if(Clk = '1') then --在小频率时钟高电平时采样,Clk频率一定

if(Cnt5 <="10001" and Cnt5>="01101") then

Sign1 <='1'; --在频率合理范围的标志信号置1

Cnt5 <= Cnt5 + '1';

elsif(Cnt5 ="11111") then --当计数器到最大值时保持,目的防止溢出

Sign1 <='0';

Cnt5 <= "11111";

else --不再合理频率范围的,标志信号置0

Sign1 <='0';

Cnt5 <= Cnt5 + '1';

end if;

else

Cnt5 <= "00000"; --计数器清零,标志信号保持

Sign1 <=Sign1;

end if;

else

Sign1 <='1';

Cnt5 <= "00000";

end if;

end if;

end process;

功能仿真和后仿真波形,总会出现计数器刚一计数时就是最大值11111,而不是从0开始逐次加1

求解:1、为什么会出现此问题,程序那里出了问题?

2、如何修改?

我要赚赏金

我要赚赏金