一个呼吸灯程序:

`timescale 1ns/ 1ps

module breath(clkn, rstn,ledn, PWMn,cntn);

input clkn;

input rstn;

output ledn;

output reg [2:0] PWMn; //原数据是【4:0】

output reg [5:0] cntn; //原数据是【23:0】

always @(posedge clkn )

begin

if(!rstn)

cntn <= 0;

else

cntn <= cntn + 1'b1 ;

end

wire [1:0] PWM_input = cntn[5]? cntn[4:3]: ~cntn[4:3]; //原数据是【3:0】【23】【22:19】【22:19】

always @(posedge clkn)

begin

if(!rstn)

PWMn <= 0;

else

PWMn <= PWMn[1:0]+PWM_input; //原数据是【3:0】

end

assign ledn = PWMn[2]; //原数据是【4】

endmodule

`resetall

不明白原理,就想在modelsim上仿真试试,把数据改了,上注释是原始数据,其中原程序中只有一个输入clkn,一个输出ledn,为方便弄清原理,我改了端口。

以下是testbench:

`timescale 1ns/ 1ps

module breaths;

reg clks;

reg rsts;

wire leds;

wire [5:0] cnts;

wire [2:0] PWMs;

breath led_inst(clks, rsts,leds, PWMs,cnts);

initial

begin

clks = 0;

while(1)

#5 clks = ~clks;

end

initial

begin

rsts = 0;

while(1)

#5 rsts = 1;

end

initial

begin

$display($time, "clks = %d rsts = %d leds = %d cnts = %d PWMs = %d",clks,rsts,leds,cnts,PWMs);

end

endmodule

`resetall

问题:

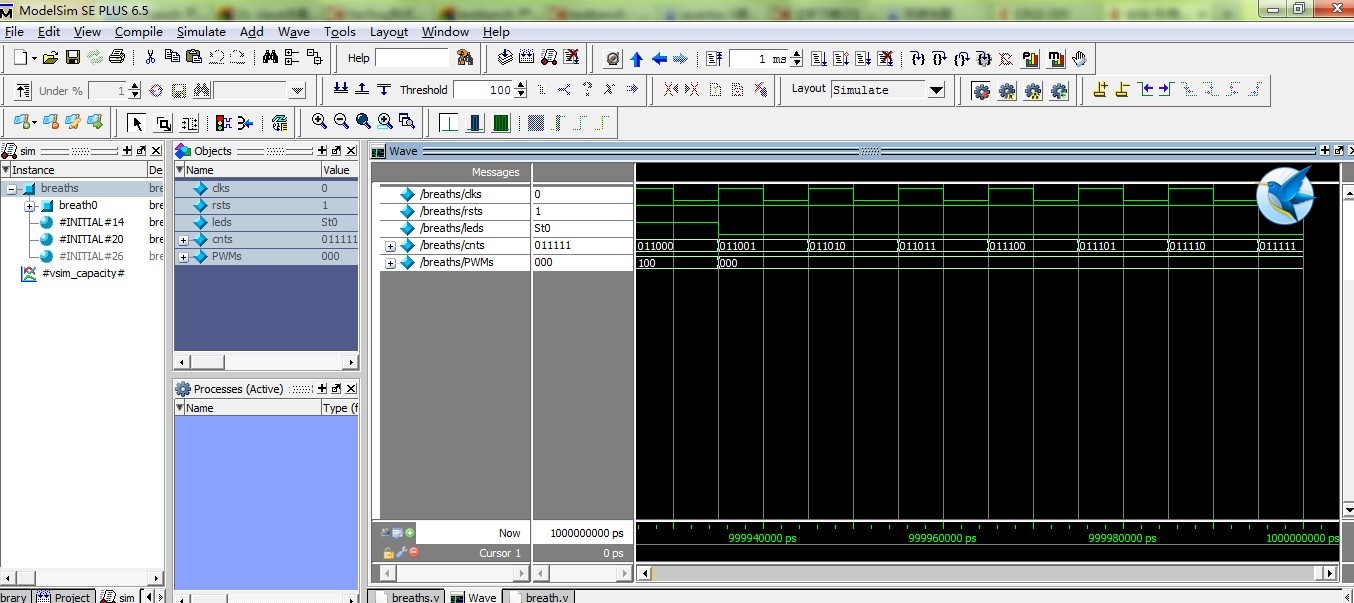

为什么display输出波形中leds,cnts,PWMs都是XXXX,如图以下是script截图:

我是选择全编译后,直接startsimulate,

求助,刚接触这个没几天,这问题弄很久了。

我要赚赏金

我要赚赏金