难得找到借口回家休息一下,学校网速太屁,电信移动这些破单位,只晓得自己捞油水,也不真真实实的犒劳下人民大众提高一下网速。 回归正题,本人是被学校拉着去参加第八届全国研究生设计大赛的,本来手头上就有两个项目,还有一篇EI文章要发,又来个坑爹的比赛。比赛规则上是说一个月时间交作品,类型主要是IC设计,其实就是说用FPGA咯。学校脱了半个月,六月中才给我们下这个比赛的要求,我从北京回来6月25号差不多才腾出时间和精力来做,7月9号就要上交作品。这搞的时间上就输了一大截,很多有基础的人不愿意比赛,要么毕业设计没做完,要么就是学车没时间。好吧,我还是用剩下将近两个星期的时间认真应付下。

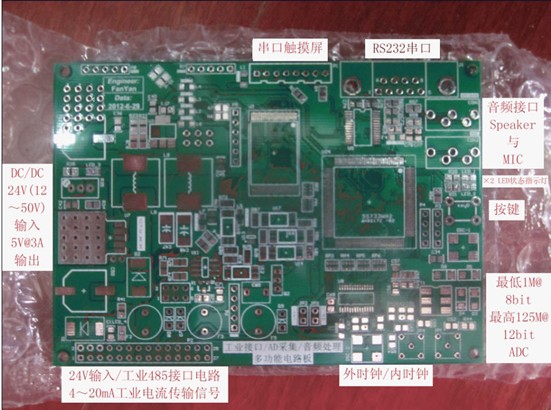

先讲我做的东西吧,发泄的话后面再说。考虑到利用我以前调过的电路和设计方案,在短时间能马上用的,和老师讨论了下,决定做个全数字FM接收机,主要核心在信号处理上面。和普通的FM收音机不同的是,这只是借助FM,88~108Mhz这个频带信号,直接中频带通采样将两个以上频道的信号同时解出来功放声音。主要是验证软件无线电的设计方法,相当于中频信号只要进入FPGA就可以做任意的实时处理,比如在雷达中通过IQ信号获得回波的相位信息,从而可以获得目标多普勒速度信息,通信领域除了能同时处理多种调制方式的信号,还可以获得采样带宽内所有的信息,再加上一些滤波器就可以做到全通采样。下面介绍实物,并把时间附上。 6月25号开始画PCB,29号投出去(48小时加急)。板子7月4号到手。如下图。

将用到的芯片焊完,并将AD调通花了大概1,2天的时间。实物图如下。

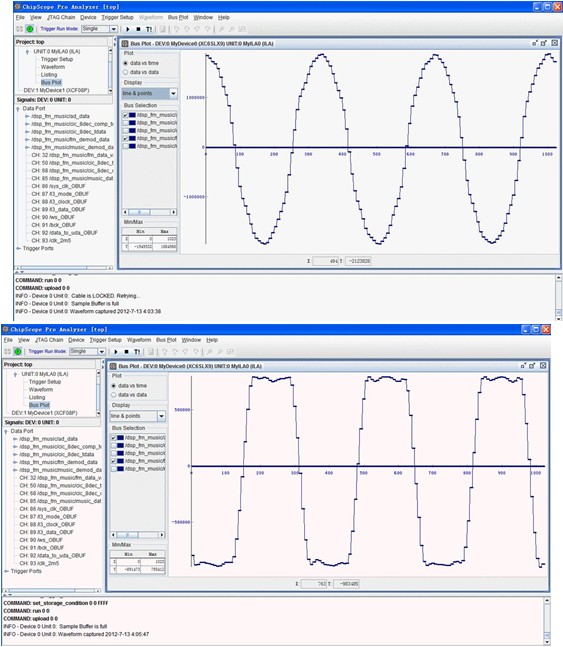

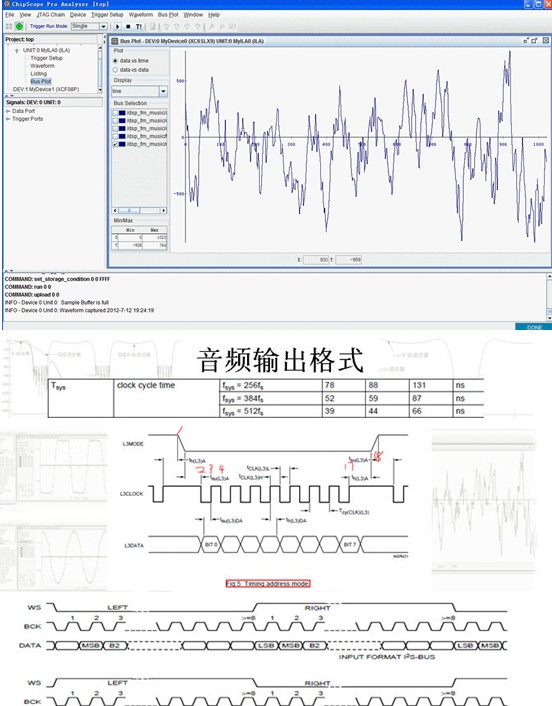

剩下的工作就是代码了。有算法部分和接口部分。算法主要是将速率为80M的已调信号数字下变频到基带IQ分量,然后两路同时滤波抽取到容易处理的速率上来,好做FM解调。然后再将解调出来的语音信号滤波抽取到和多功能语音芯片匹配的采样率上。这其中,最麻烦的肯定是抽取滤波器的结构设计。因为用的不是高端、大容量、信号处理FPGA(其实就是没他们有钱,理解),乘法资源有限只有16个DSP48。采用CIC加半带的结构做一个通道的资源都不够。因此,我采用的全是CIC加补偿的结构,之所以要补偿是因为5级CIC要抽取128倍,通带畸变严重。该结构还有个缺点就是截止频率不好控制。但是对这种信号强度比较强的广播信号还是可以的。算法设计的细节在答辩演讲PPT里面有全面的框图和图片,有兴趣的朋友可以下下来看看。方波和正弦波调制信号的解调波形通过chipscope抓出用256个窗口看到的波形如下。

解调完成后就是与音频接口速率匹配的问题了。我在调试的过程中是一步一步找方案的,并不是首先就订好这样的方案,个人认为实际操作中最难做到的是这一步。因为解调出来得到波形当时有点小激动,认为直接在解调前抽取到语音芯片速率上再解调就行了。事实根本不可行。比如说在94M上的FM信号,频偏75Khz,调制信号最小能到1mV。这样的信号直接抽取到音频39khz的速率上,解出来的调制信号肯定失真了。所以当时走了点小弯路,理解错误。幸好经过仔细分析,深刻理解了FM信号的性质后,才走出这个误区。所以,信号处理要发挥真正的作用,第一步是深刻理解待处理的信号。FM解调出来的速率是625khz,继续抽取16倍就是39khz,这就刚好和语音芯片UDA1341耦合上了。然而这个抽取同样不好用半带。因为FPGA里面不复用资源的话半带总是要花乘法器的。而低速率的CIC抽取特性明显降低。所以,这里的也不能直接用CIC抽取到39Khz上来,我才用的CIC加补偿做8倍抽取,最后高性能的FIR做2倍抽取。指标就看PPT。chipscope抓出来的语音调制信号波形如下图。

这时的速率就是39khz,最后只剩接口了。比赛那几天我是先把I2S接口调完再调算法。幸运的是,最后一天,也就是7月9号早上,连续通宵了3个晚上把算法调完。直接连上之前调好的接口模块,声音就出来了。其实有点运气,因为I2S和L3BUS接口我之前没有调过,比赛比的是时间,尤其是电子设计这样的比赛。有经验的老师都知道,成熟的东西,用过的最保险最可靠,凡是半路出家的东西调出来的机会都比较渺茫。下面是接口协议图,也就是UDA1341格式图。朋友们可以掂量掂量自己在1天的时间里面能不能弄出来。

到这里,我的作品算是介绍完了。7月10号早上把以前学弟弄的D类音频功率放大器加上,把声音功放出来就写文档和PPT,这又是艰难的几个通宵一直到比赛的当天7月14号没有好好睡一觉。好了。我现在要说说这比赛坑爹的地方,虽然是中国电子协会牵头的比赛,也吸引了全国所有的重点高校,但是比赛结果和学生(注意是学生)的水平让我有点失望。结果对我其实是比较满足的,得了个西南赛区一等奖(注:我们赛区有6个特等奖,只有特等奖才有机会参加到东大举行的总决赛,赛区一等奖直接是全国三等奖)。毕竟我的成本才500块钱左右,还包括七七八八的车费什么的。本来计划最高也就是这个奖,不然白忙活了2个星期。我的失望有这么几个地方。

第一:重点高校拿出来的参赛作品,我不说全部吧,至少大多数都不可能是学生在比赛规定的一个月能做出来的。有的甚至是做了3,4年的国家项目或者公司项目。我要透露的是我前面一组的作品,直接说了吧,重庆某高校一个队伍直接拿整个团队(说是10个人)的4G项目下来,三个学生可以说什么都不懂,没有系统概念,还和评委摆起来了。这个现象不是一个两个,而是普遍。自己画了PCB的队伍不到三分之一。所以我认为这就是坑爹,砸钱的比赛。不是我不想搬,其实我也想啊,问题是做雷达的难不成还把整机搬下来演示一遍。那这样比下去就是比哪个学校钱多了。这就牵出来下一个失望了。

第二:比赛太过于开放,嵌入式也来抽热闹,自动化也来,医疗也来。这就造成了平台的不一致。部分是基于FPGA的,部分是基于ARM的,甚至单片机的也有。这如何比,功能可以自定,像我这个作品,直接把射频前端取了功能上就是全的。也是因为太过开放,很多队伍就偷懒直接拿做好的硬件,而且是高速、高端、高价的硬件平台,这就叫低速、低端、低价的平台队伍望尘莫及啊。

第三:过分强调创新导致电子设计比赛成展示台。创新固然重要,但是创新有大有小,过分强调创新的结果就是只看功能和应用,没有考虑到功能和应用看不到的创新点,也就算法的创新没有考察。我感受很深,答辩时专家没有一个问过我算法部分,只问我AD指标,大概的功能和用途。据我所知,网上有人贴除了日本FPGA大赛的获奖作品,同样也是全数字FM接收机,他们还只只做了解调,但他们没用用到IP核,有算法创新一样拿大奖。当然我有我的考虑,我的NCO不用IP核可以采用线性预测的方案,这我很早以前验证过,只需一个2阶矩阵运算,只需要两个乘法器和一个减法器,精度可以任意设定。其他的可以用现有方案。但是幸好我没有再花时间去弄这个东西,因为弄了也比不过他们说的功能不完整。

该说的都说完了,把一些照片贴出来有兴趣的朋友劲量留言说说感想,大家互相交流。这个板子我准备到网上卖给对FPGA有兴趣的初学者,因为我是过来人,我知道开发板真正有用的地方,尤其是对FPGA开发板,千万不能陷入单片机的开发模式。这个板子提供了我平时常用的接口,而且可以开发soc,并留有串口触摸屏接口。触摸功能我在microblaze里面已经实现了。不过有一点不好,就是成本相比有点高,因为有高速AD,毕竟这只是给我个人以后项目调试用的用的板子。同时,板子上还有工业485接口电路(千万别将485接口理解成一个芯片了)和4~20mA电流传输接口,分立元件,有80us光耦、Linear的串行DAC、以及电压电流转换电路。该接口电路是国外某著名公司用了几十年产品上的电路。以后有时间,我再改一改,把其他有用的电路加进来。而且把射频前端做好一起和大家分享经验,共同进步。

我要赚赏金

我要赚赏金