刚开始接触CPLD,我现在用的开发环境是ISE14.2版本的,学习期间问题多多啊,捡其中一两个来向大家请教,请大家多多指导。

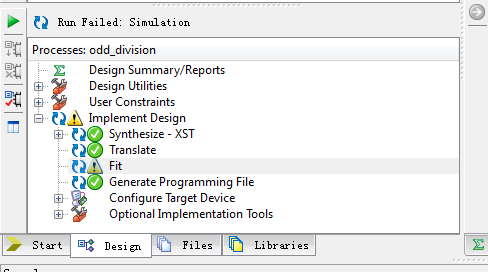

1.如下图,程序没有问题,为什么FIT不成功,CPLD编程在哪一步对管脚进行设置,也就是自己定义的和实际芯片管脚联系起来?

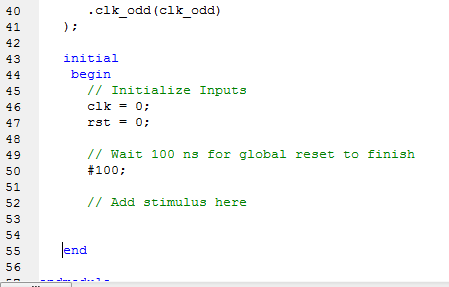

2.如下图,怎么对已有的程序进行仿真验证,用自带的软件怎么编写仿真程序?

这个界面不是绑定ucf的,你可以找个例程的ucf,用文本打开看看

头尾固定,中间部分自己定义修改

#PACE: Start of Constraints generated by PACE

#PACE: Start of PACE I/O Pin Assignments

NET "FPIO2" LOC = "p10" ;

#PACE: Start of PACE Area Constraints

#PACE: Start of PACE Prohibit Constraints

#PACE: End of Constraints generated by PACE

说白了,ucf就是芯片物理管脚和内部分配的关联性

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |

| 【S32K3XX】LIN 通讯模块使用被打赏¥31元 | |

| 【FreeRtos】FreeRtos + MPU模块的配置使用被打赏¥32元 | |