给欲从事芯片开发工作的同学,来点科普知识。

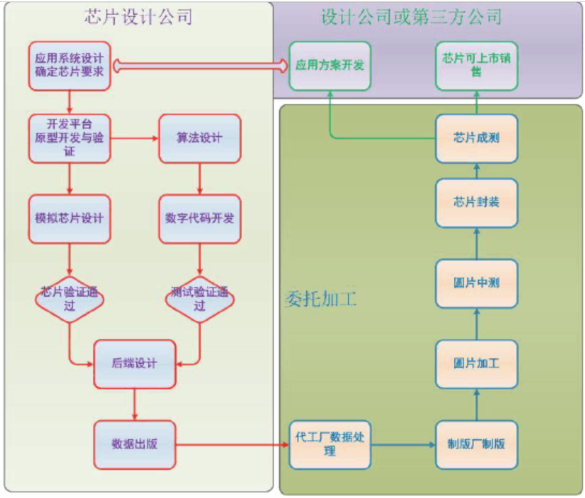

一款芯片的设计开发,首先是根据产品应用的需求,设计应用系统,来初步确定应用对芯片功能和性能指标的要求,以及哪些功能可以集成,哪些功能只能外部实现,芯片工艺及工艺平台的选择,芯片管脚数量,封装形式等等,达到整个应用系统的成本低性能高,达到最优的性价比。

之后,进入系统开发和原型验证阶段。根据芯片的框架结构,采用分立元件设计电路板,数字系统一般用FPGA开发平台进行原型开发和测试验证(常见的FPGA有XILINX和ALTERA两个品牌。

模拟芯片的设计,验证手段主要是根据工艺厂提供的参数模型来仿真,最终能达到的性能指标只能通过真实的投片,进行验证设计;而数字系统设计一般可通过计算机仿真和FPGA系统,进行充分的设计验证,然后可以直接投片。因此数模混合的芯片产品开发,一般需要模拟模块先投片验证,性能指标测试通过后,然后再进行整体投片。系统开发和原型验证通过后,就进入芯片版图设计实现阶段,就是数字后端、与模拟版图拼接。版图设计过程中,要进行设计验证,包括DRC、LVS、ANT、后仿真等等。芯片版图通过各种仿真验证后就可以生成GDS文件,发给代工厂(或者制版厂),就是常说的tapeout了。

代工厂数据处理,拿到GDS数据后,需要再次进行DRC检查,然后数据处理,版层运算,填充测试图形等操作,之后发给制版厂开始制版。制版完成后,光刻版交给代工厂就可以进行圆片加工了。圆片加工完成后,送至中测厂进行中测,也叫晶圆测试(Chip Test,简称CP)。中测完成,圆片上打点标记失效的管芯,交给封装厂。封装厂进行圆片减薄、贴膜、划片、粘片、打线、注塑、切金、烘干、镀锡等等操作后,封装完成。目前封装技术比较成熟,常见封装良率在99.5%以上,甚至99.9%以上。

芯片有些功能和性能在中测时无法检验的,需要进行成测(Final Test,简称FT)。成测完成的芯片,即可入产品库,转入市场销售了。

芯片的研发过程,是一个多次循环迭代的过程。测试验证过程中发现问题,就需要返回修改设计,然后再次测试验证;后端版图实现过程中,如果时序、功耗、面积、后仿真等通不过,也可能要返回原始设计进行修改;芯片投片出来后,测试性能指标和可靠性达不到设计要求,需要分析定位问题,修改设计,再次投片验证,等等。芯片研发环节多,投入大,周期长。任何一个细节考虑不到或者出错,都有可能导致投片失败;技术研发充满了不确定性,可能导致时间拖延及投片失败。因此,一个成熟产品的研发,可能需要多次的投片验证,导致周期很长。现在芯片设计的规模比较大,系统复杂,为了减小投片风险,系统设计和测试验证的工作十分重要,一方面依靠强大的EDA工具,另一方面依靠经验和人员时间投入。

芯片转入量产后,如果成品率不稳定或低于预期,需要与代工厂分析原因,进行工艺参数调整,多次实验后,找到最稳定的工艺窗口,提高芯片的可靠性和良率,降低成本。

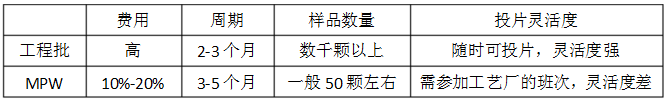

常见的芯片投片方式说明 芯片常用投片方式有工程批(FULLMASK)和多项目晶圆(Multi Project Wafer,简称MPW)两种方式。

随着制造工艺水平的提高,在生产线上制造芯片的费用不断上涨,一次0.6微米工艺的工程批生产费用就要20-30万元,而一次0.18微米工艺的工程批生产费用则需要60-120万元,如果采用高阶工艺,试验片成本更会呈几何倍数提高。如果设计中存在问题,那么制造出来的所有芯片将全部报废。

MPW就是将多个具有相同工艺的集成电路设计放在同一晶圆片上流片,流片后,每个设计品种可以得到几十片芯片样品,这一数量对于设计开发阶段的实验、测试已经足够。而实验费用就由所有参加MPW的项目按照芯片面积分摊,成本仅为工程批的10%-20%,极大地降低新产品开发成本和开发风险。MPW一般由工艺厂组织,每年定期有班次。

虽MPW降低了集成电路研发阶段的费用门槛,但也伴随着一些投片灵活度低、生产周期长、单位面积有限制等制约因素。 具体的投片方式,需要根据设计成功率、资金预算、时间周期来具体选择。

两种投片方式对比表:

我要赚赏金

我要赚赏金