本文核心议题:本文是对Intel 22nm三栅技术的后续追踪报道,为此,这里搜集了多位业界观察家、分析家对此的理解和意见,以便大家I更深入的了解ntel 22nm三栅技术。

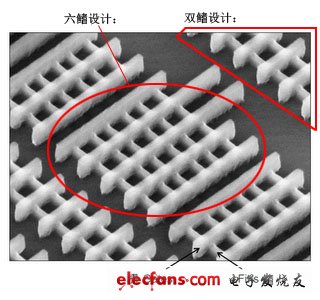

鳍数可按需要进行调整(Intel 22nm三栅发布会原图)

传统的平面型晶体管沟道位于栅电极的下方,沟道为平面2D结构,平行与衬底,沟道的导通由单个栅电极控制;而三栅垂直型晶体管的沟道位置则位于垂直于衬底的鳍(Fin)中,沟道所在位置的鳍周围被三个栅极从三个方向包围。不仅如此,还可以采用将多个鳍并联在一起,以增加晶体管的总电流的方法来提升管子的性能。按照Intel自己的说法,比较32nm平面型器件,22nm三栅管子在性能同等的条件下功耗可减少50%以上,而在功耗同等的条件下性能则可增加37%左右。

尽管Intel并不愿意过早透露22nm三栅制程的较多技术和制造细节,但Intel高管Mark Bohr已经承认采用22nm三栅技术其制造成本约比32nm技术提高了2-3%左右,这部分增加的成本主要是由于蚀刻/淀积技术的复杂化而造成的--这主要是由于Intel仍然使用193nm液浸式光刻+双重成像(简称193i+DP)方法来制造22nm三栅晶体管,因此需要采用更复杂的技术手段来保证193i+DP的可用性。不过,Deutsche Bank的分析师Ross Seymore认为这部分成本的增加,应该可以用晶体管密度提升带来的成本下降来弥补。

Gartner的分析师Dean Freeman则强调22nm三栅工艺的实现主要对三个方面提出了相对较高的要求,一是光刻技术方面的要求,二是控制鳍侧壁离子注入掺杂均匀性的要求,三是鳍边缘粗糙度控制方面的要求。

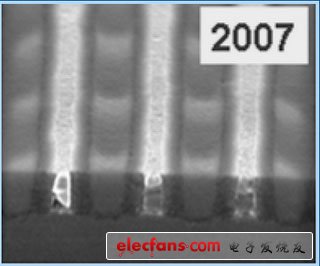

Intel2006年曾对外展示过的采用HKMG工艺制作的三栅晶体管的纵切图片

Intel2007年曾对外展示过的采用HKMG工艺制作的三栅晶体管的图片栅极截面

而 Linley Group的分析师 Tom Halfhill则进一步把这些制程技术方面的要求细化为了四个方面:一是垂直鳍需要将较厚的硅层蚀刻后得到,二是要保证鳍尺寸均一性对蚀刻技术的要求更高,三是要在鳍的三面淀积栅极金属材料的要求(Intel 22nm三栅制程采用了HKMG栅极,仍然采用Gate last工艺制作),四则是为了保证过程控制,有更严格的测试和验证工艺方面的要求。在22nm三栅晶体管中,鳍和金属栅的厚度,宽度尺寸会影响晶体管的性能。最后,按照电路设计的要求,还需要能够灵活控制鳍的尺寸来实现某部分电路性能,延迟参数和功耗的优化。

Chipworks的Dick James则强调三栅制程需要采用全新的电路设计和布局准则,因此不太可能使用三栅SRAM+逻辑电路采用平面型晶体管结构的混合工艺(实际上此前的报道已经证实了这一点)。另外,Freeman还评价说,赶在应用EUV之前启用三栅工艺,还可以避免同时启用EUV和三栅两种新技术导致的麻烦。

我要赚赏金

我要赚赏金