Viterbi译码原理

Viterbi译码算法(简称VA算法)是由Viterbi在1967年首先提出的,它是一种针对卷积码的最大似然译码算法。他不是在网格图上依次比较所有的可能路径,而是接受一段,计算、比较一段,保留最有可能的路径,从而达到整个码序列是一个最大似然序列。Viterbi译码算法优点是在码的约束比较小时,它比序列译码算法效率更高、速度更快,译码器也较简单。缺点就是随着约束长度的增加算法的复杂度增加很快。约束长度N为7时要比较的路径就有64条,为8时路径变为128条。(2(N-1))。所以Viterbi译码一般应用在约束长度小于10的场合中。虽然有许多算法降低了复杂性、减少了运算量,但它们必然以牺牲性能为代价。本文研究的出发点是立足于不降低算法性能,寻求在实现最大似然译码时的优化方法。而这点我们主要是通过与硬件实现相结合做到的。Viterbi算法主要由路径度量的“加比选”运算、度量的更新、路径的更新、最大似然路径的回溯过程组成。

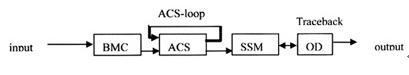

Viterbi译码算法流程图如图1所示。

图1 Viterbi译码算法处理流程

我要赚赏金

我要赚赏金