数字波形是逻辑电平对时间的图形表示。通常,我们将只有两个离散值的波形称之为脉冲波形,在这一点上脉冲波形与数字波形是一致的,只不过数字波形用逻辑电平表示,而脉冲波形用电压值表示而已。

与模拟波形的定义相同,数字波形也有周期性和非周期性之分。图1.1.4表示了这两类数字波形:

周期性数字波形同样用周期T或频率f来描述;而脉冲波形的频率常称为脉冲重复率PRR--Pulse Repetition Rate。

脉冲波形的参数:

脉冲宽度:tw表示,表示脉冲作用的时间;

占空比:q,表示脉冲宽度tw占整个周期T的百分数,常用下式来表示:

占空比是一个重要参数,其定义同样适用于数字波形。

图1.1.5表示两种数字波形及其周期、频率、脉冲宽度和占空比:

例题1.1.1设周期性数字波形的高电平持续6ms,低电平持续10ms

,求占空比q?

解:根据给定的高电平持续时间有tw= 6ms,而高电平与低电平持续时间之和即为周期T

所以有 T=6ms+10ms=16ms

到目前为止,我们所讨论的数字波形都是理想波形,然而实际的数字系统中,数字波形的升降都要经历一段时间,也就是说波形存在上升时间tr和下降时间tf 。

上升时间tr的定义是:从脉冲幅值的10%到90%所经历的时间;下降时间tf的定义刚好相反:从脉冲幅值的90%到10%所经历的时间。tr和tf的典型值约为几个纳秒(ns),视不同类型的器件和电路而异。

脉冲宽度的定义是脉冲幅值为50%时前后两个时间点所跨越的时间。非理想脉冲如图1.1.6所示:

例题1.1.2 试绘出一脉冲波形,设它的占空比为50%,脉冲宽度 tw=100ns,上升时间tr=10ns,下降时间tf=20ns。

解:根据题意,可绘出脉冲波形如下:

图1.1.7 例1.1.2的波形图

图1.1.7 例1.1.2的波形图

一般情况下波形的上升或下降时间均要比高电平或低电平的持续时间要小很多,画波形的目的主要是为了了解高、低电平所经历的时间。因此在理想波形中就只有高、低电平,而忽略了上升和下降时间

。本课程中所用的数字波形将采用理想波形。

当然,实际中碰到的波形,不管从示波器上来看,其上升沿和下降沿是多么的直,tr和tf都不可能为零,只是在数字电路中,只需关注逻辑电平的高低,因此在画波形时只需画出高低电平所经历的时间即可,无需画出上升沿和下降沿。

(a)

(b)

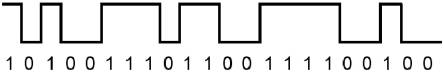

图1.1.8 用逻辑1和0表示的二值位行图

(a) 对称方波 (b) 二值数据

上图为一个二值位形图,其中1或1占用的最小时间称为位时间

,也就是1位数据所占用的时间。我们将每秒钟所传输的位数称为数据率或比特率。

例题1.1.3 某通信系统每秒中传输1.544兆位数据,求每位数据的时间。

解:根据题意,只需将1.544M倒数,即可求得每位数据的时间为:

举例来说,象图1.1.8b中看到的22位的二值位形图,如果每一位数据所占用的时间是648ns,则22位共占用14256ns,也就是14.256微秒,而其数据率就是1.544兆。

在设计数字集成电路时,有时为了分析各种信号之间的逻辑关系

,需要将多个数字波形按时间排列在一起,用来表明相互间的时间关系,我们将这样一种关系图称为时序图(Timing diagram)。

时序图中的每一个波形都被称为时间信号。时序图被广泛运用在设计数字集成电路中,在设计存储器、微处理机等数字应用电路时均须附有时序图,以便数字系统的分析、应用和设计。

图1.1.9就是一个时序图的例子:

图1.1.9 数字时序图

图中CP为时钟脉冲信号,用作系统中的时间参考信号,一般由石英晶体振荡器来产生,如图所示波形为对称方波。关于图中各个波形的具体作用,将在以后的课程加以介绍.

我要赚赏金

我要赚赏金