LVDS系统设计

LVDS系统的设计要求设计者应具备超高速单板设计的经验并了解差分信号的理论。设计高速差分板并不困难,下面将简要介绍一下各注意点。

PCB板

(A)至少使用4层PCB板(从顶层到底层):LVDS信号层、地层、电源层、TTL信号层;

(B)使TTL信号和LVDS信号相互隔离,否则TTL可能会耦合到LVDS线上,最好将TTL和LVDS信号放在由电源/地层隔离的不同层上;

(C)使LVDS驱动器尽可能地靠近连接器的LVDS端,即尽可能减小线路距离;

(D)保证LVDS器件电源质量;使用分布式的多个电容来旁路LVDS设备,表面贴电容靠近电源/地层管脚放置;

(E)电源层和地层应使用粗线;

(F)保持PCB地线层返回路径宽而短;

(G)连接两个系统的地层;

板上导线

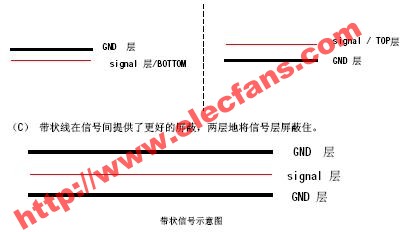

(A) 微带传输线(microstrip)和带状线(stripline)都有较好性能;

(B) 微带传输线的优点:一般有更高的差分阻抗、不需要额外的过孔;

差分线

(A)使用与传输媒质的差分阻抗和终端电阻相匹配的受控阻抗线,并且使差分线对离开集成芯片后立刻尽可能地相互靠近(距离小于10mm),这样能减少反射并能确保耦合到的噪声为共模噪声;

(B)使差分线对的长度相互匹配以减少信号扭曲,防止引起信号间的相位差而导致电磁辐射;

(C)不要仅仅依赖自动布线功能,而应仔细修改以实现差分阻抗匹配并实现差分线的隔离;

(D)尽量减少过孔和其它会引起线路不连续性的因素;

(E)避免将导致阻值不连续性的90°走线,使用圆弧或45°折线来代替;

(F)在差分线对内,两条线之间的距离应尽可能短,以保持接收器的共模抑制能力。在印制板上,两条差分线之间的距离应尽可能保持一致,以避免差分阻抗的不连续性。

终端

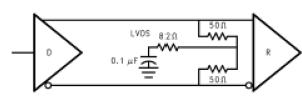

(A)使用终端电阻实现对差分传输线的最大匹配,阻值一般在90~130Ω之间,系统也需要此终端电阻来产生正常工作的差分电压;

(B)最好使用精度1~2%的表面贴电阻跨接在差分线上,必要时也可使用两个阻值各为50Ω的电阻,并在中间通过一个电容接地,以更好滤去共模噪声。如采用电缆传输信号时候,若环境干扰大,就可以用此方式。

未使用的管脚

所有未使用的LVDS接收器输入管脚悬空,所有未使用的LVDS和TTL输出管脚悬空,将未使用的TTL发送/驱动器输入和控制/使能管脚接电源或地。

媒质(电缆和连接器)选择

(A)仅就减少噪声和提高信号质量而言,平衡电缆(如双绞线对)通常比非平衡电缆好;

(B)电缆长度小于0.5m时,大部分电缆都能有效工作;距离在0.5m~10m之间时,CAT 3(Categiory 3)双绞线对电缆效果好、便宜并且容易买到;距离大于10m并且要求高速率时,建议使用CAT 5双绞线对。

在噪声环境中提高可靠性设计

LVDS 接收器在内部提供了可靠性线路,用以保护在接收器输入悬空、接收器输入短路以及接收器输入匹配等情况下输出可靠。但是,当驱动器三态或者接收器上的电缆没有连接到驱动器上时,它并没有提供在噪声环境中的可靠性保证。在此情况下,电缆就变成了浮动的天线,如果电缆感应到的噪声超过LVDS内部可靠性线路的容限时,接收器就会开关或振荡。如果此种情况发生,建议使用平衡或屏蔽电缆。

根据实际情况,正确分析设计发送/接收器的“门控端”,使发送接收数据器受控,当不需要建立发送/接收链路时候,关闭接收器是避免干扰的有效途径。

我要赚赏金

我要赚赏金