一、P0端口的结构及工作原理

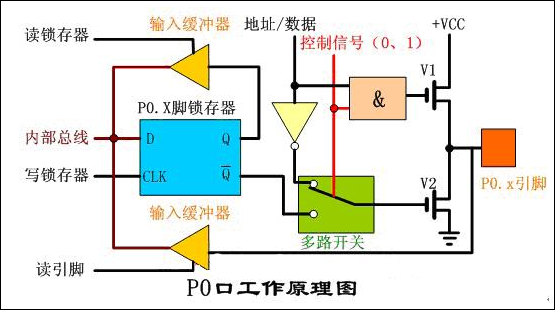

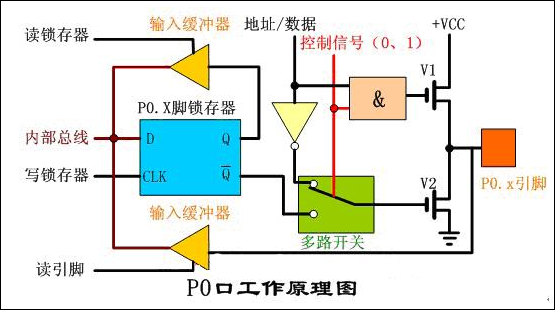

P0端口8位中的一位结构图见下图:

由上图可见,P0端口由锁存器、输入缓冲器、切换开关、一个与非门、一个与门及场效应管驱动电路构成。再看图的右边,标号为P0.X引脚的图标,也就是说P0.X引脚可以是P0.0到P0.7的任何一位,即在P0口有8个与上图相同的电路组成。

下面,我们先就组成P0口的每个单元部份跟大家介绍一下:

先看输入缓冲器:在P0口中,有两个三态的缓冲器,在学数字电路时,我们已知道,三态门有三个状态,即在其的输出端可以是高电平、低电平,同时还有一种就是高阻状态(或称为禁止状态),大家看上图,上面一个是读锁存器的缓冲器,也就是说,要读取D锁存器输出端Q的数据,那就得使读锁存器的这个缓冲器的三态控制端(上图中标号为‘读锁存器’端)有效。下面一个是读引脚的缓冲器,要读取P0.X引脚上的数据,也要使标号为‘读引脚’的这个三态缓冲器的控制端有效,引脚上的数据才会传输到我们单片机的内部数据总线上。

D锁存器:构成一个锁存器,通常要用一个时序电路,时序的单元电路在学数字电路时我们已知道,一个触发器可以保存一位的二进制数(即具有保持功能),在51单片机的32根I/O口线中都是用一个D触发器来构成锁存器的。大家看上图中的D锁存器,D端是数据输入端,CP是控制端(也就是时序控制信号输入端),Q是输出端,Q非是反向输出端。

对于D触发器来讲,当D输入端有一个输入信号,如果这时控制端CP没有信号(也就是时序脉冲没有到来),这时输入端D的数据是无法传输到输出端Q及反向输出端Q非的。如果时序控制端CP的时序脉冲一旦到了,这时D端输入的数据就会传输到Q及Q非端。数据传送过来后,当CP时序控制端的时序信号消失了,这时,输出端还会保持着上次输入端D的数据(即把上次的数据锁存起来了)。如果下一个时序控制脉冲信号来了,这时D端的数据才再次传送到Q端,从而改变Q端的状态。

多路开关:在51单片机中,当内部的存储器够用(也就是不需要外扩展存储器时,这里讲的存储器包括数据存储器及程序存储器)时,P0口可以作为通用的输入输出端口(即I/O)使用,对于8031(内部没有ROM)的单片机或者编写的程序超过了单片机内部的存储器容量,需要外扩存储器时,P0口就作为‘地址/数据’总线使用。那么这个多路选择开关就是用于选择是做为普通I/O口使用还是作为‘数据/地址’总线使用的选择开关了。大家看上图,当多路开关与下面接通时,P0口是作为普通的I/O口使用的,当多路开关是与上面接通时,P0口是作为‘地址/数据’总线使用的。

输出驱动部份:从上图中我们已看出,P0口的输出是由两个MOS管组成的推拉式结构,也就是说,这两个MOS管一次只能导通一个,当V1导通时,V2就截止,当V2导通时,V1截止。

与门、与非门:这两个单元电路的逻辑原理我们在第四课数字及常用逻辑电路时已做过介绍,不明白的同学请回到第四节去看看。

前面我们已将P0口的各单元部件进行了一个详细的讲解,下面我们就来研究一下P0口做为I/O口及地址/数据总线使用时的具体工作过程。

1、作为I/O端口使用时的工作原理

P0口作为I/O端口使用时,多路开关的控制信号为0(低电平),看上图中的线线部份,多路开关的控制信号同时与与门的一个输入端是相接的,我们知道与门的逻辑特点是“全1出1,有0出0”那么控制信号是0的话,这时与门输出的也是一个0(低电平),与让的输出是0,V1管就截止,在多路控制开关的控制信号是0(低电平)时,多路开关是与锁存器的Q非端相接的(即P0口作为I/O口线使用)。

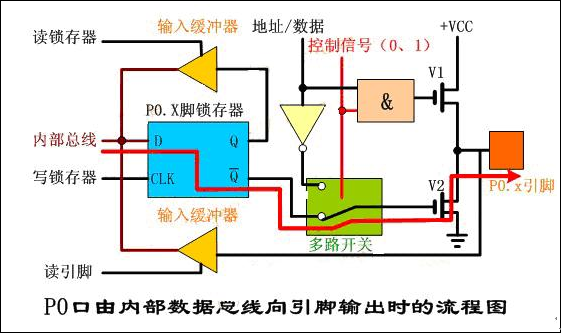

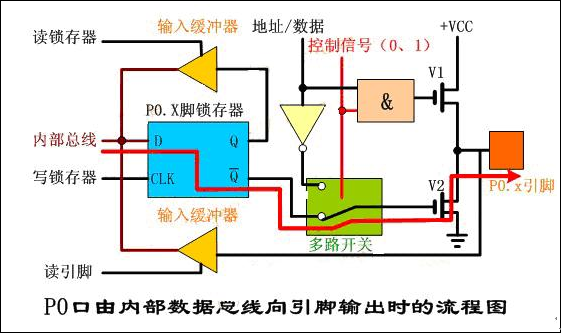

P0口用作I/O口线,其由数据总线向引脚输出(即输出状态Output)的工作过程:当写锁存器信号CP 有效,数据总线的信号→锁存器的输入端D→锁存器的反向输出Q非端→多路开关→V2管的栅极→V2的漏极到输出端P0.X。前面我们已讲了,当多路开关的控制信号为低电平0时,与门输出为低电平,V1管是截止的,所以作为输出口时,P0是漏极开路输出,类似于OC门,当驱动上接电流负载时,需要外接上拉电阻。

下图就是由内部数据总线向P0口输出数据的流程图(红色箭头)。

P0口用作I/O口线,其由引脚向内部数据总线输入(即输入状态Input)的工作过程:

数据输入时(读P0口)有两种情况

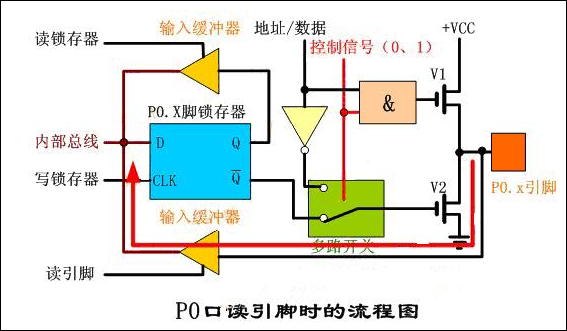

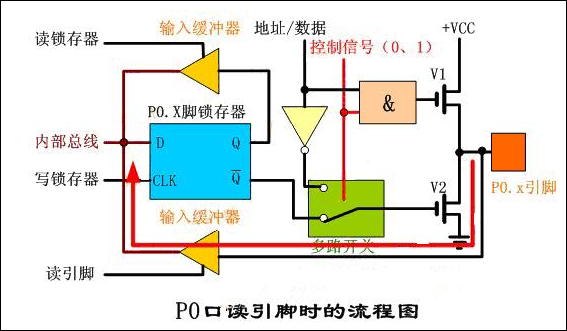

1、读引脚

读芯片引脚上的数据,读引脚数时,读引脚缓冲器打开(即三态缓冲器的控制端要有效),通过内部数据总线输入,请看下图(红色简头)。

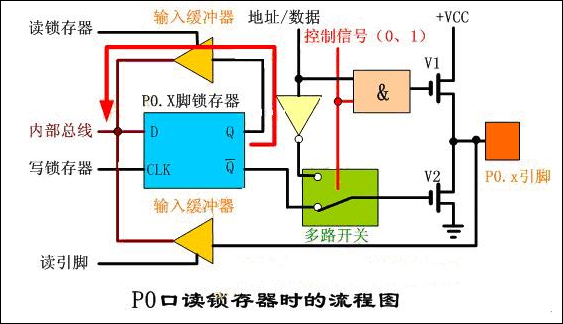

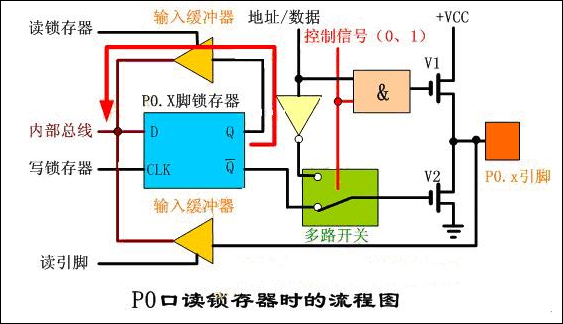

2、读锁存器

通过打开读锁存器三态缓冲器读取锁存器输出端Q的状态,请看下图(红色箭头):

在输入状态下,从锁存器和从引脚上读来的信号一般是一致的,但也有例外。例如,当从内部总线输出低电平后,锁存器Q=0,Q非=1,场效应管T2开通,端口线呈低电平状态。此时无论端口线上外接的信号是低电乎还是高电平,从引脚读入单片机的信号都是低电平,因而不能正确地读入端口引脚上的信号。又如,当从内部总线输出高电平后,锁存器Q=1,Q非=0,场效应管T2截止。如外接引脚信号为低电平,从引脚上读入的信号就与从锁存器读入的信号不同。为此,8031单片机在对端口P0一P3的输入操作上,有如下约定:凡属于读-修改-写方式的指令,从锁存器读入信号,其它指令则从端口引脚线上读入信号。

读-修改-写指令的特点是,从端口输入(读)信号,在单片机内加以运算(修改)后,再输出(写)到该端口上。下面是几条读--修改-写指令的例子。

ANL P0,#立即数 ;P0→立即数P0

ORL P0,A ;P0→AP0

INC P1 ;P1+1→P1

DEC P3 ;P3-1→P3

CPL P2 ;P2→P2

这样安排的原因在于读-修改-写指令需要得到端口原输出的状态,修改后再输出,读锁存器而不是读引脚,可以避免因外部电路的原因而使原端口的状态被读错。

P0端口是8031单片机的总线口,分时出现数据D7一D0、低8位地址A7一AO,以及三态,用来接口存储器、外部电路与外部设备。P0端口是使用最广泛的I/O端口。

2、作为地址/数据复用口使用时的工作原理

在访问外部存储器时P0口作为地址/数据复用口使用。

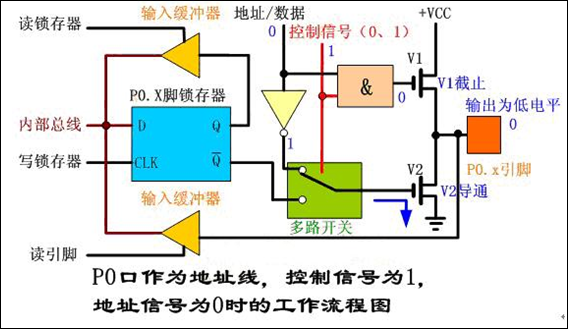

这时多路开关‘控制’信号为‘1’,‘与门’解锁,‘与门’输出信号电平由“地址/数据”线信号决定;多路开关与反相器的输出端相连,地址信号经“地址/数据”线→反相器→V2场效应管栅极→V2漏极输出。

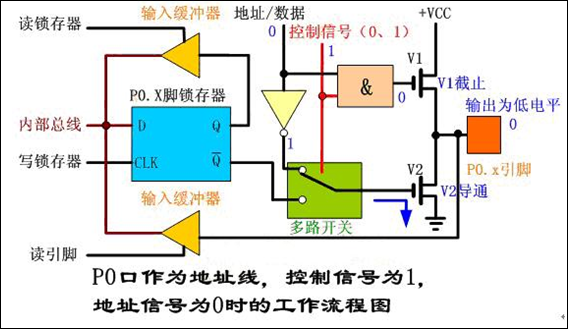

例如:控制信号为1,地址信号为“0”时,与门输出低电平,V1管截止;反相器输出高电平,V2管导通,输出引脚的地址信号为低电平。请看下图(兰色字体为电平):

反之,控制信号为“1”、地址信号为“1”,“与门”输出为高电平,V1管导通;反相器输出低电平,V2管截止,输出引脚的地址信号为高电平。请看下图(兰色字体为电平):

可见,在输出“地址/数据”信息时,V1、V2管是交替导通的,负载能力很强,可以直接与外设存储器相连,无须增加总线驱动器。

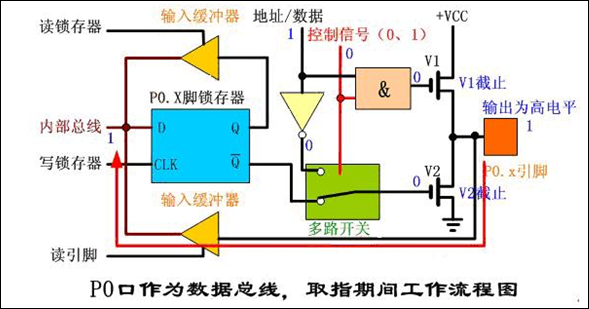

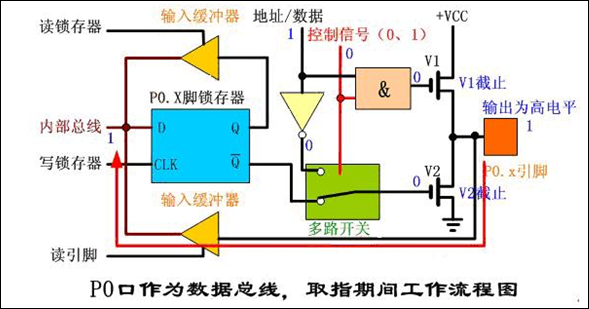

P0口又作为数据总线使用。在访问外部程序存储器时,P0口输出低8位地址信息后,将变为数据总线,以便读指令码(输入)。

在取指令期间,“控制”信号为“0”,V1管截止,多路开关也跟着转向锁存器反相输出端Q非;CPU自动将0FFH(11111111,即向D锁存器写入一个高电平‘1’)写入P0口锁存器,使V2管截止,在读引脚信号控制下,通过读引脚三态门电路将指令码读到内部总线。请看下图

如果该指令是输出数据,如MOVX @DPTR,A(将累加器的内容通过P0口数据总线传送到外部RAM中),则多路开关“控制”信号为‘1’,“与门”解锁,与输出地址信号的工作流程类似,数据据由“地址/数据”线→反相器→V2场效应管栅极→V2漏极输出。

如果该指令是输入数据(读外部数据存储器或程序存储器),如MOVX A,@DPTR(将外部RAM某一存储单元内容通过P0口数据总线输入到累加器A中),则输入的数据仍通过读引脚三态缓冲器到内部总线,其过程类似于上图中的读取指令码流程图。

通过以上的分析可以看出,当P0作为地址/数据总线使用时,在读指令码或输入数据前,CPU自动向P0口锁存器写入0FFH,破坏了P0口原来的状态。因此,不能再作为通用的I/O端口。大家以后在系统设计时务必注意,即程序中不能再含有以P0口作为操作数(包含源操作数和目的操作数)的指令。

|

我要赚赏金

我要赚赏金