1 系统硬件设计

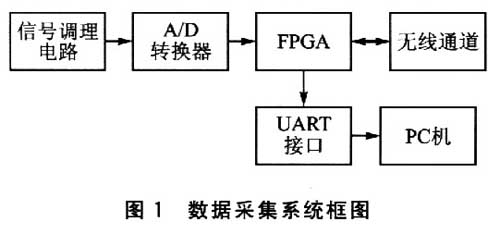

数据采集系统框图如图1所示。

图中,A/D转换器采用了TI公司的16位逐次逼近型ADS8344;FPGA主要用于控制ADC的启动、停止和查询ADC状态等,同时对数据进行高速数据缓冲、异步数据编解码、无线信道编解码等数据处理。

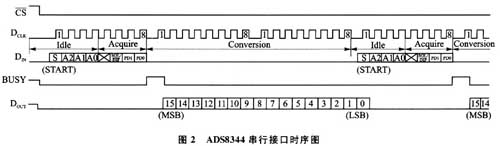

1.1 主要芯片ADS8344

ADS8344是一款高性能、低功耗的ADC,采用2.7~5V单电源供电,最大采样频率为100 kHz,信噪比达84dB,自带采样/保持电路,包含8个单端模拟输入通道(CH0~CH7),也可合成为4个差分输入。参考电压VRFF的范围为500mV~VCC,相应的每个模拟通道的输入为0V~VREF,DS8344是通过三线SPI接口与FPGA相互通信的,数据从DIN引脚输入到8位只写控制寄存器。当FPGA读取完ADC上次转换

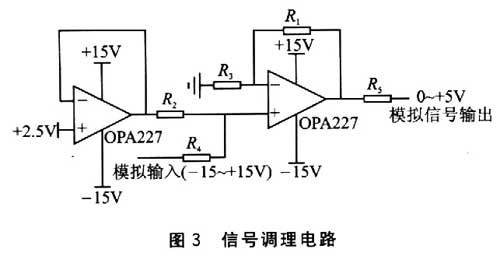

1.2 信号调理电路

数据采集前端的调理电路如图3所示。2个运放选用的是TI公司的精密仪表放大器OPA277。由于输入模拟电压信号为双极性,范围为一15~+5 V,而ADX8344模拟输入通道为O V~VREF(本系统是+5 V),所以必须对输入信号进行单极性转换。

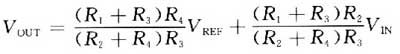

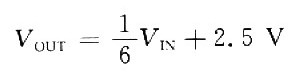

其传递函数为:

式中:VOUT为转换后的单极性电压信号;VREF由电压基准源提供,在图中是+2.5V;VIN为输入的一15~+15 V电压信号。当R3=6R1、R4=6R2时,传递函数可化简为:

可见,传递函数是线性函数。只要正确选择精确的电阻值,一15~+15 V电压信号可线性转换为O~+5V,从而保证了系统的精度。

1.3 无线通道

本系统是按用户的要求设计开发的,其中,无线通道是由用户提供的。本系统采用的无线通道是点对点传输,传输距离最远达40 km,传输速率最高达11 Mbps,对标准异步串口数据是透明传输。A/D电路输出的数据经FPGA高速数据缓冲、异步数据编码、无线信道编码等数据处理后,送到无线通道进行无线传输。远端的无线接收机接收到数据后送到FPGA进行无线信道解码、异步数据解码等处理,恢复A/D采样数据,然后或者送到D/A电路进行模拟量输出,或者重新进行异步数据编码送到PC机,由PC机对数据做进一步的分析处理。

2 软件设计

本系统的软件设计包括了FPGA硬件描述语言编程和PC机应用程序。

2.1 FPGA编程

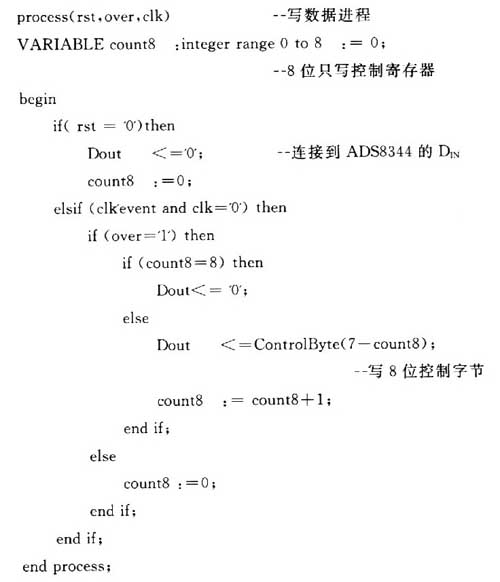

FPGA编程使用VHDL语言,主要包括对ADS8344的数据读写、异步数据编解码等。使用FPGA很容易实现SPI接口间的通信,对ADS8344的数据读写仅用两个进程就可以实现。部分程序如下:

(1)写数据进程

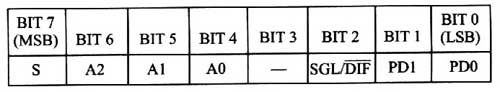

程序中的8位控制字节是在另一进程中根据用户要求进行配置的。控制寄存器格式如下:

控制寄存器各位的功能说明如下:

-

S——控制字节开始位。为高时,才表示输入的字节有效。

-

A2~AO——模拟输入通道选择位。

-

SGL/DIF——模拟通道输入方式选择位。为高时,为单端输入i为低时,为双端差分输入。

- PDl~DO——功率管理选择位。

我要赚赏金

我要赚赏金