一、网表导入常见错误查找:

1、打开netin。log文件

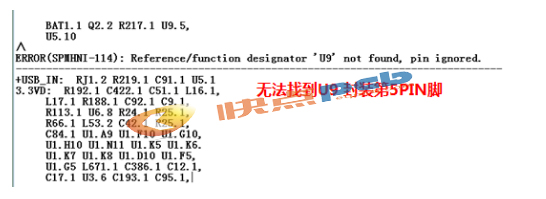

2、查找关键字error,如下图:

查找1

查找2

查找3

二、网表导入常见错误处理:

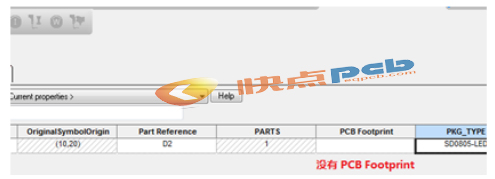

1、器件没指定PCB Footprint,是由于原理图中信息缺少造成的。如下图:

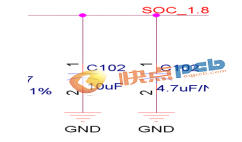

2、器件位号定义重复,如下图:

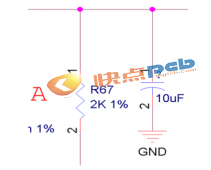

3、器件位号信息缺失,如下图:

小结:在原理图设计工具中修改常见错误,重复网表导入操作,直到netin。log文件中没有error为止,才算完成原理图网表成功导入PCB设计工具。

下期介绍预告:PCB结构设计,请同学们持续关注【快点PCB学院】公众号。

我要赚赏金

我要赚赏金