ADSP-BF531 / ADSP-BF532 / ADSP-BF533处理器是Blackfin®系列产品的成员,包括

ADI公司/英特尔微信号架构(MSA)。Blackfin处理器结合了双MAC最先进的信号处理引擎,干净,正交RISClike微处理器指令集的优点,以及单指令,多数据(SIMD)多媒体功能集成指令集架构。 中国IC交易网 中国ICPDF网

ADSP-BF531 / ADSP-BF532 / ADSP-BF533处理器是完全代码和引脚兼容,仅在尊重方面有所不同他们的表现和片上记忆。

特征

高达600 MHz的高性能Blackfin处理器两个16位MAC,两个40位ALU,四个8位视频ALU,40位移位器类似RISC的寄存器和指令模型,易于编程和编译友好的支持高级调试,跟踪和性能监控。

可编程片上稳压器

160球CSP_BGA,169球PBGA和176引脚LQFP包

外设

并行外设接口PPI,支持ITU-R 656视频数据格式2个双通道,全双工同步串口,支持8个立体声I2S频道

2个内存到内存的DMA

8个外设DMA

SPI兼容端口

三个支持PWM的32位定时器/计数器实时时钟和看门狗定时器

32位核心计时器

多达16个通用I / O引脚(GPIO)

UART支持IrDA

事件处理程序

调试/ JTAG接口

片上PLL能够倍频

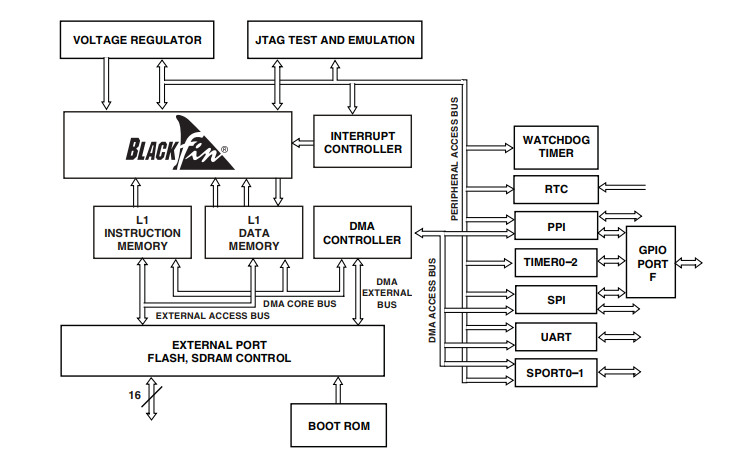

功能框图

便携式低功耗架构

Blackfin处理器提供世界一流的电源管理和表现。Blackfin处理器设计低电源和低压设计方法和功能

动态电源管理 - 能够改变操作的电压和频率,从而显着降低整体性能能量消耗。改变电压和频率即可与仅改变操作频率相比,导致功耗显着降低。这个转换为便携式设备的更长电池寿命。

系统集成ADSP-BF531 / ADSP-BF532 / ADSP-BF533处理器是高度集成的片上系统解决方案,适用于下一代数字通信和消费类多媒体应用。通过结合行业标准接口和高性能信号处理核心,用户可以开发经济高效的解决方案,无需昂贵的成本外部组件。系统外围设备包括UART端口,SPI端口,两个串行端口(SPORT),四个通用定时器(三个具有PWM功能),一个实时时钟,一个看门狗定时器和并行外设接口。

处理器外围设备

ADSP-BF531 / ADSP-BF532 / ADSP-BF533处理器包含一组丰富的外设,通过几个连接到内核高带宽总线,提供系统配置的灵活性以及出色的整体系统性能(参见上图中的功能框。通用外围设备包括UART,定时器等功能具有PWM(脉冲宽度调制)和脉冲测量功能能力,通用I / O引脚,实时时钟和a看门狗定时器。这组功能满足各种各样的功能典型的系统支持需求,并由系统增强部件的扩展能力。除了这些通用外围设备外,处理器还包含高速串行设备和并行端口,用于连接各种音频,视频和调制解调器编解码器一个灵活的中断控制器管理来自片上外设的中断或外部来源;和电源管理控制功能在许多应用场景中定制处理器和系统的性能和功耗特性。

除通用I / O外,所有外设都是实时的时钟和定时器由灵活的DMA结构支持。还有一个专用的独立存储器DMA通道处理器的各种存储空间之间的数据传输,包括外部SDRAM和异步存储器。多个运行频率高达133 MHz的片上总线足够在所有片上和外部外设上保持处理器内核运行的带宽。

处理器包括支持的片上稳压器处理器的动态电源管理功能。该电压调节器提供一系列核心电压电平VDDEXT。电压调节器可以在用户旁边旁路自由裁量权。

BLACKFIN处理器核心

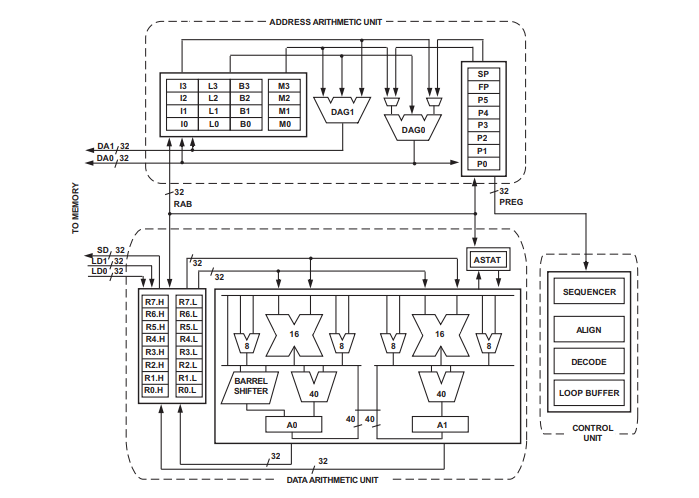

如下图1所示,Blackfin处理器内核包含两个16位乘法器,两个40位累加器,两个40位ALU,四个视频ALU和一个40位移位器。计算单元处理来自的8位,16位或32位数据注册文件。

计算寄存器文件包含8个32位寄存器。什么时候对16位操作数数据执行计算操作寄存器文件作为16个独立的16位寄存器运行。所有计算操作的操作数来自多端口寄存器文件和指令常量字段。每个MAC可以在每个MAC中执行16位乘16位乘法循环,将结果累积到40位累加器中。有符号和无符号格式,舍入和饱和度支持的。

ALU执行一组传统的算术和逻辑对16位或32位数据的操作。另外,很多特别的包括指令以加速各种信号处理任务。这些包括位操作,如字段提取和种群计数,模232乘法,除原语,饱和和舍入,以及符号/指数检测。这套视频指令包括字节对齐和打包操作,带有削波的16位和8位加法,8位平均值操作,8位减法/绝对值/累加(SAA)操作。还提供了比较/选择和向量搜索说明。

对于某些指令,可以在寄存器对上同时执行两个16位ALU操作(16位高半部分和计算寄器的16位低半部分。四路16位操作可以使用第二个ALU。40位移位器可以执行移位和旋转并用于支持规范化,字段提取和字段存储说明。

程序定序器控制指令执行的流程,包括指令对齐和解码。对于程序流控制,音序器支持PC相对和间接条件跳转(使用静态分支预测),和子程序调用。提供硬件以支持零开销循环。该架构完全互锁,意味着程序员在执行时不需要管理管道具有数据依赖性的指令。地址算术单元提供两个地址,用于从存储器同时进行双重提取。它包含一个多端口寄存器文件由四组32位索引组成,修改,长度和基址寄存器(用于循环缓冲)和8附加的32位指针寄存器(用于C风格的索引堆栈操作)。

Blackfin处理器支持改进的哈佛架构与分层记忆结构相结合。1级(L1)存储器通常是在完整处理器上运行的存储器速度很慢或没有延迟。在L1级别,指令记忆只保留说明。两个数据存储器成立数据和专用的暂存器数据存储器存储堆栈和局部变量信息。此外,还提供了多个L1存储器模块,提供了一个可配置的SRAM和缓存组合。内存管理单元(MMU)为个人提供内存保护可以在核心上运行并可以保护系统的任务从非预期的访问中注册。该架构提供三种操作模式:用户模式,管理员模式和仿真模式。用户模式有限制访问某些系统资源,从而提供一个受保护的软件环境,而管理员模式有不受限制地访问系统和核心资源。

Blackfin处理器指令集已经过优化16位操作码代表最常用的指令,从而产生出色的编译代码密度。复杂DSP指令被编码为32位操作码,代表功能齐全的多功能说明书。 Blackfin处理器支持有限的多发布功能,其中32位指令可以与两个16位指令并行发出,允许程序员使用a中的许多核心资源单指令周期。

Blackfin处理器汇编语言使用代数语法来简化编码和可读性。这个架构一直都是经过优化,可与C / C ++编译器配合使用,从而实现快速有效的软件实施。

记忆体系结构

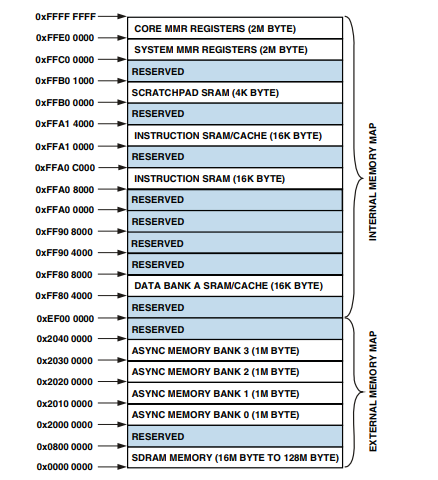

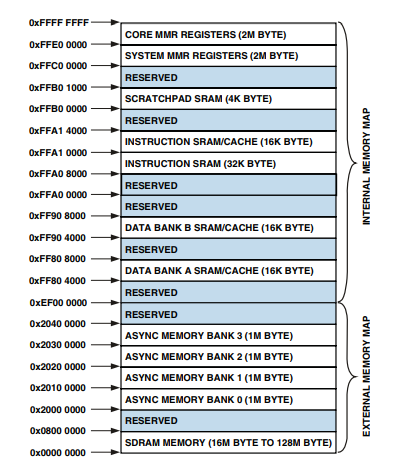

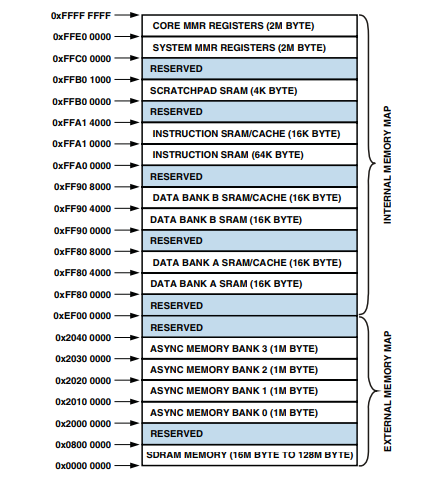

ADSP-BF531 / ADSP-BF532 / ADSP-BF533处理器可查看内存作为单个统一的4G字节地址空间,使用32位地址。所有资源,包括内部存储器,外部内存和I / O控制寄存器占用了不同的部分这个共同的地址空间。这个的记忆部分地址空间以分层结构排列以提供一些非常快速,低延迟的良好成本/性能平衡片上存储器作为缓存或SRAM,更大,更低成本和性能片外存储器系统。见下图2,图3,图4.L1内存系统是主要的最高性能Blackfin处理器可用的内存。

Blackfin处理器核心

ADSP-BF531内部/外部存储器映射

ADSP-BF532内部/外部存储器映射

ADSP-BF533内部/外部存储器映射

处理器上的事件控制器处理所有异步和处理器的同步事件。ADSP-BF531 /ADSP-BF532 / ADSP-BF533处理器提供事件处理它支持嵌套和优先级。嵌套允许多个事件服务例程同时处于活动状态。优先级确保服务于更高优先级的事件服务于较低优先级事件的优先级。控制器支持五种不同类型的事件:

仿真 - 仿真事件会导致处理器进入进入仿真模式,允许命令和控制处理器通过JTAG接口。

重置 - 此事件重置处理器。

不可屏蔽中断(NMI) - NMI事件可以是由软件看门狗定时器或NMI生成输入信号到处理器。 NMI事件经常发生用作断电指示器以启动系统的有序关闭。

例外 - 与程序同步发生的事件流程(即,在指令之前进行例外处理允许完成)。数据对齐等条件违规和未定义的指令会导致异常。

中断 - 与程序异步发生的事件流。它们是由输入引脚,定时器等引起的外围设备,以及明确的软件指令。

每个事件类型都有一个相关的寄存器来保存返回地址和相关的事件返回指令。什么时候触发一个事件,处理器的状态保存在

主管堆栈。

ADSP-BF531 / ADSP-BF532 / ADSP-BF533处理器事件控制器由两个阶段组成,核心事件控制器(CEC)和系统中断控制器(SIC)。 核心事件控制器与系统中断控制器配合使用以确定优先级并控制所有系统事件。从概念上讲,中断了外设进入SIC,然后直接路由到CEC的通用中断。

我要赚赏金

我要赚赏金