MaxLinear,Inc.是联网家庭、有线和无线基础设施以及工业和多市场应用所需的低功耗 CMOS 射频(RF) 和模拟/混合信号 (AMS) 集成电路 (IC) 的先锋厂商。其关注的市场焦点之一是数字信号处理(DSP) 片上系统 (SoC) 解决方案,旨在满足大规模云和企业数据中心对高速光互连的需求。服务器市场的 DSP 芯片预期要工作 10 年或更长时间,这意味着可靠性和可制造性都是成功设计流程的关键组成部分。

MaxLinear 的布局布线 (P&R) 工程师致力于实现高可靠性和可制造性的 SoC 设计,同时优化其功耗、性能和面积 (PPA) 设计目标。但是,布局布线过程中的自动化设计增强可能产生版图差异,导致芯片级复杂设计规则检查 (DRC) 错误,例如顶层/知识产权 (IP) 模块接口,或导致“最后一英里”功能/时序工程变更单 (ECO) 错误。此类错误非常复杂,通常要求布局布线工程师在 DRC 收敛期间手动调试和纠正。

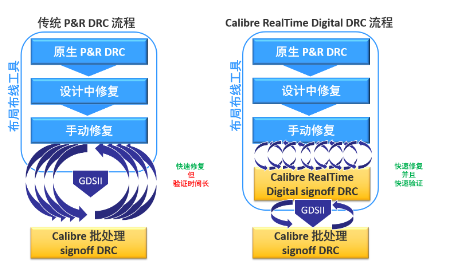

传统上,批处理 DRC 流程是为全芯片运行而设置的,并未根据选定设计窗口中的即时 DRC 反馈而优化。为了最大限度地减少调试时间,同时又能确保达到“设计即正确”的精度,MaxLinear 的布局布线工程师看到了一个优化数字实现物理验证流程的机会,那就是使用Calibre™ RealTime Digital设计中 DRC,在布局布线环境中实现按需 Calibre signoff DRC。

MAXLINEAR 的设计挑战与机遇

MaxLinear 的芯片既有模拟元器件,又有数字元器件。模拟设计的布线连接不需要很多层,因此MaxLinear 优化了可用于布线的层数,从而降低总体制造成本。然而,通过均匀地增加所有层的布线密度,这种层优化可能使得数字设计的布线变得困难,通常需要额外的 signoff DRC 迭代才能实现DRC 收敛。

MaxLinear 的芯片既有模拟元器件,又有数字元器件。模拟设计的布线连接不需要很多层,因此MaxLinear 优化了可用于布线的层数,从而降低总体制造成本。然而,通过均匀地增加所有层的布线密度,这种层优化可能使得数字设计的布线变得困难,通常需要额外的 signoff DRC 迭代才能实现DRC 收敛。

虽然原生 P&R DRC 引擎可解决大部分 DRC 错误,但其无法处理的违规通常是复杂的 DRC 错误,需要很多次手动调试和 DRC 迭代才能修复;此过程可能需要数周时间,因而可能导致流片日程延迟。使用本地窗口修复之后,设计人员必须手动将 P&R 数据与 IP 数据合并以生成合并的 GDSII/OASIS 数据库,然后运行完整批处理 DRC 来验证此修复。如果 DRC 错误仍然存在,则必须一次又一次地重复这个耗时的过程。

令这些挑战更加复杂的是,P&R DRC 解决方案无法识别和标记某些类型的 DRC 违规,例如下列原因引起的违规:

■手动 DRC 错误修复

■最后时刻的功能/时序 ECO 变更

■为提高 DFM 得分而进行的最终过孔交换

MaxLinear 需要一种流程来缩短其 DRC 收敛时间,并使其设计人员能够同时满足设计可靠性和可制造性要求以及 PPA 设计目标。Calibre RealTime Digital 接口可直接调用 Calibre 分析引擎来运行晶圆代工厂认证的 signoff Calibre 规则集(图 1)。这些引擎在正在编辑的形状附近执行快速增量检查,从而提供有关 DRC 违规的近乎即时的反馈。P&R 域中的这种即时反馈使得 MaxLinear 工程师能够以signoff 级质量实现和检查修复,而无需进行完整的 DRC 迭代。由于能够执行快速的 signoff 级质量的设计中修复,他们得以缩短 DRC 收敛周期时间,同时仍有把握确保 Calibre signoff DRC。

我们将从三方面探讨 MaxLinear 如何使用 Calibre RealTime Digital 设计中 DRC 来提升设计质量,同时缩短设计收敛时间。

图 1:传统 P&R DRC 流程与 Calibre RealTime Digital 设计中signoff DRC 流程的比较。

过孔选择

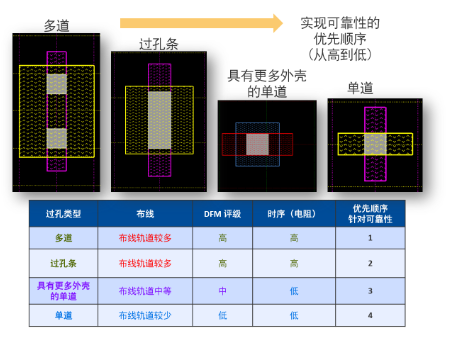

MaxLinear 的布局布线工程师力图实现至少 80% 的可制造性设计 (DFM) 过孔得分,这是一项艰巨的任务,需要在给定设计区域内选择最佳过孔类型以满足时序、可靠性和可制造性要求。

晶圆代工厂通常提供四类过孔:单道过孔、带扩展外壳的单道过孔、过孔条过孔和多道过孔(图 2)。在这些过孔类型中,单道过孔最不好,因为它有高电阻,这对时序会产生负面影响,而且其可制造性设计 (DFM) 评级很低。不过,它确实会使布线更轻松,从而减少DRC 错误。与单道过孔相比,在过孔周围添加更多外壳的单道过孔具有更好的 DFM 评级,但仍有很高的电阻。过孔条提供较高的 DFM 评级和更好的时序(由于电阻减小),但会使布线更具挑战性。多道过孔具有两种过孔形状(因而在制造过程中不太可能使过孔失效),可靠性最好,而且性能也优于两种单道过孔。但是,与过孔条过孔一样,多道过孔也存在布通率挑战。

图 2:改善 DFM 评级和时序的首选过孔类型。

MaxLinear 在数字设计实现期间的首选解决方案是最大限度地使用多道过孔和过孔条过孔,以确保设计满足时序、可靠性和可制造性要求。但是,多道过孔和过孔条类型均会使设计布线更困难,产生必须手动修复的复杂 DRC 错误,导致 DRC 收敛时间延长。借助 Calibre RealTime Digital 设计中DRC,工程师可以换入新的过孔类型,在本地窗口中使用设计中 DRC 来捕获由交换产生的 DRC 错误,予以修复,然后再次快速验证以确保版图无 DRC 错误。完成多次过孔交换之后,通常是在他们确信接近或已经实现目标 DFM 得分时,他们还可以重新检查 DFM 得分。

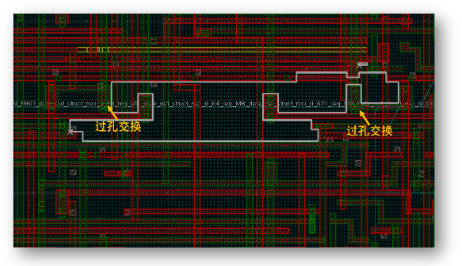

多重曝光违规

将单道过孔换成多道过孔或过孔条过孔,也可能导致多重曝光(MP) 违规(图 3),修复起来既困难又耗时,因为此类违规通常涉及对版图执行假设分析,需要手动修复,然后等待 DRC 反馈。通过 Calibre RealTime Digital 接口,布局布线工程师可以快速且有把握地执行假设分析,为每次手动编辑提供即时 signoff DRC 反馈,从而帮助布局布线工程师确定并实施针对 MP 违规的最优修复。

图 3:单道过孔换成多道过孔导致 MP 违规,对此可以手动修复并利用 Calibre RealTime Digital 设计中 DRC 立即进行验证,从而提高设计人员的生产率并缩短总 DRC 收敛时间。

……………………

我要赚赏金

我要赚赏金