[经验]深度刨析:时序约束和数字系统相互之间有着怎样的影响

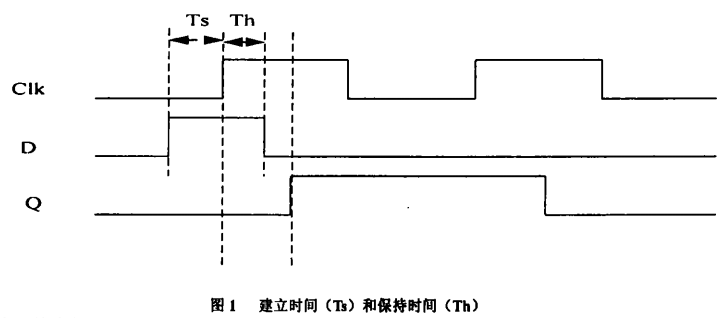

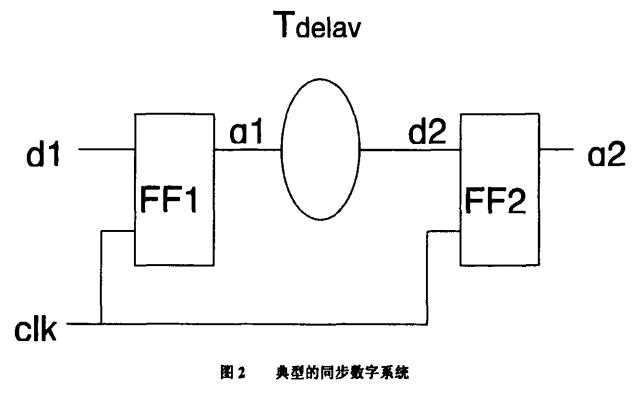

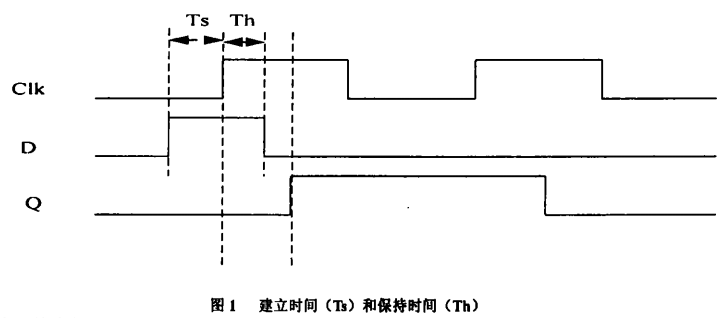

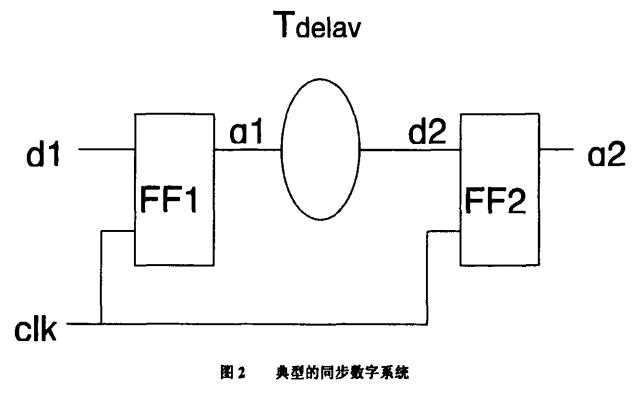

在进行数字电路系统的设计时,时序是否能够满足要求直接影响着电路的功能和性能。本文首先讲解了时序分析中重要的概念,并将这些概念同数字系统的性能联系起来,最后结合FPGA的设计指出时序约束的内容和时序约束中的注意事项。一、时序分析中的重要概念在数字系统中有两个非常重要的概念:建立时间和保持时间,其示意图如图1所示。一个数字系统能否正常工作跟这两个概念密切相关。只有建立时间和保持时间都同时得到满足时,数字系统才能可靠的、正常的工作。 当寄存器的建立时间或保持时间不能得到满足时,寄存器有可能会进入亚稳态( Metastable)。亚稳态是一种电压的中间态,假设寄存器的输出电压大于3V判决为逻辑1,小于0.3V判决为逻辑0,那么电压处于0.3V到3V之间并且能够短时间稳定的状态就是亚稳态。寄存器在进入亚稳态一段时间后会回复到正常的状态,但是有可能回到逻辑1的状态,也有可能回到逻辑0的状态。这种不确定性就有可能引起数字系统的错误。建立时间和保持时间是一个寄存器的固有属性,是由其内部的结构、工艺等因素决定的,因而在进行数字系统设计时只能通过改变电路结构使其满足建立时间和保持时间的要求,而不能改变建立时间和保持时间的值。二、建立时间和保持时间对电路性能的影响首先来看一个典型的同步数字系统的示意图,见图2。

当寄存器的建立时间或保持时间不能得到满足时,寄存器有可能会进入亚稳态( Metastable)。亚稳态是一种电压的中间态,假设寄存器的输出电压大于3V判决为逻辑1,小于0.3V判决为逻辑0,那么电压处于0.3V到3V之间并且能够短时间稳定的状态就是亚稳态。寄存器在进入亚稳态一段时间后会回复到正常的状态,但是有可能回到逻辑1的状态,也有可能回到逻辑0的状态。这种不确定性就有可能引起数字系统的错误。建立时间和保持时间是一个寄存器的固有属性,是由其内部的结构、工艺等因素决定的,因而在进行数字系统设计时只能通过改变电路结构使其满足建立时间和保持时间的要求,而不能改变建立时间和保持时间的值。二、建立时间和保持时间对电路性能的影响首先来看一个典型的同步数字系统的示意图,见图2。

关键词:

深度

刨析

时序

约束

数字

系统

相互之间

有着

当寄存器的建立时间或保持时间不能得到满足时,寄存器有可能会进入亚稳态( Metastable)。亚稳态是一种电压的中间态,假设寄存器的输出电压大于3V判决为逻辑1,小于0.3V判决为逻辑0,那么电压处于0.3V到3V之间并且能够短时间稳定的状态就是亚稳态。寄存器在进入亚稳态一段时间后会回复到正常的状态,但是有可能回到逻辑1的状态,也有可能回到逻辑0的状态。这种不确定性就有可能引起数字系统的错误。建立时间和保持时间是一个寄存器的固有属性,是由其内部的结构、工艺等因素决定的,因而在进行数字系统设计时只能通过改变电路结构使其满足建立时间和保持时间的要求,而不能改变建立时间和保持时间的值。二、建立时间和保持时间对电路性能的影响首先来看一个典型的同步数字系统的示意图,见图2。

当寄存器的建立时间或保持时间不能得到满足时,寄存器有可能会进入亚稳态( Metastable)。亚稳态是一种电压的中间态,假设寄存器的输出电压大于3V判决为逻辑1,小于0.3V判决为逻辑0,那么电压处于0.3V到3V之间并且能够短时间稳定的状态就是亚稳态。寄存器在进入亚稳态一段时间后会回复到正常的状态,但是有可能回到逻辑1的状态,也有可能回到逻辑0的状态。这种不确定性就有可能引起数字系统的错误。建立时间和保持时间是一个寄存器的固有属性,是由其内部的结构、工艺等因素决定的,因而在进行数字系统设计时只能通过改变电路结构使其满足建立时间和保持时间的要求,而不能改变建立时间和保持时间的值。二、建立时间和保持时间对电路性能的影响首先来看一个典型的同步数字系统的示意图,见图2。

我要赚赏金

我要赚赏金