STM32的通用定时器和高级定时器除了支持单向的向上或向下计数模式外,还支持中心对齐计数模式,即一个计数周期内分别由向上计数和向下计数两个过程组成。在基于计数器的中心对齐计数模式做定时器的比较输出功能时,又进一步衍生出三种中心对齐计数模式,分别是中心对齐计数模式1/2/3。具体通过寄存器TIMx_CR1里面的CMS[1:0]选择。

既然一次基于中心对齐计数模式的完整计数周期包含向上、向下两个计数过程,那么对给定的比较寄存器CCR的值在(0,ARR)范围时,一个周期内就会发生两次匹配事件,即出现CNT=CCR的两个时间点,对于这两次匹配事件最终是否完成比较事件标志的置位而触发中断或DMA,可以根据应用需求选择不同的中心对齐计数模式来决定。

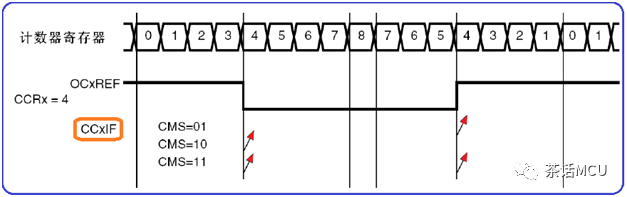

在STM32各系列参考手册中关于定时器描述部分都有类似下面的一副图,是关于不同中心对齐计数模式下发生匹配事件后的比较事件标志的置位情况的直观展示。

这里CCR=4,ARR=8, 我们来一起看看。

当选择中心对齐计数模式1时,只在向下计数过程中发生匹配动作时才置位比较事件标志CC4IF; 当选择中心对齐计数模式2时,只在向上计数过程中发生匹配动作时才置位比较事件标志CC4IF; 当选择中心对齐计数模式3时,在向上/向下计数过程中发生匹配动作时都会置位比较事件标志CC4IF。当然,比较事件标志被置位时可以触发中断或DMA请求。

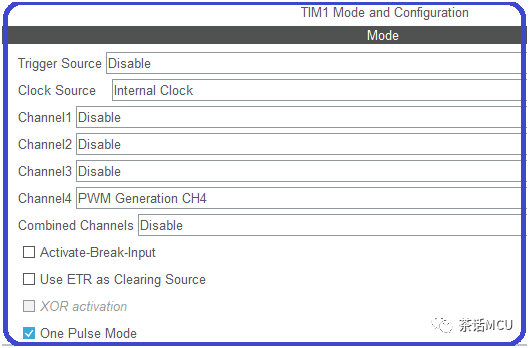

这里我们不妨使用STM32的TIM1的CH4做个验证性测试,看看在一个中心对齐计数周期内,通过选取不同的中心对齐模式下发生比较中断的次数。【这点不管哪个STM32系列都一样】

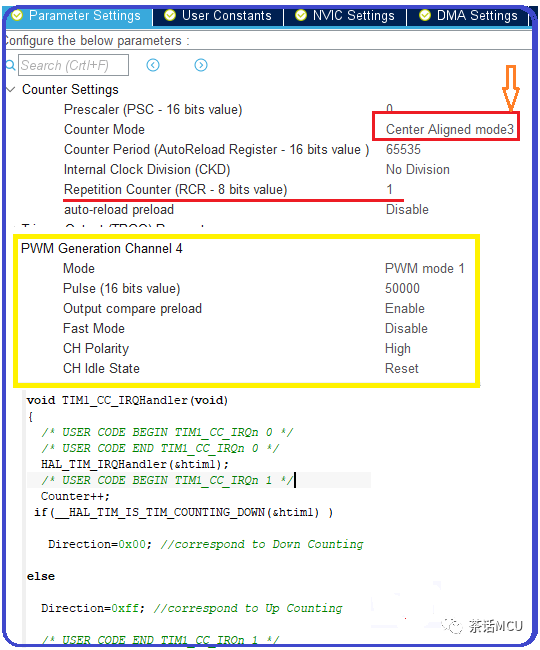

基于上面的配置及处理代码,我们只调整中心对齐计数模式,看看在一个中心对齐计数周期内比较中断的响应情况。【Counter表示进入比较中断的次数,DirecTIon表示发生比较中断时计数方向,0表示当前属向下计数过程,0xff表示向上计数过程】

测试结果在上图很清晰了,无须赘述。

那么,关于这个定时器特性有什么用呢,这个不好说,毕竟具体应用往往丰富多彩而千变万化。总之,书到用时方恨少嘛,了解各个外设的特性是我们灵活运用的基础和前提。比方在马达应用中,这个特性可能就用得着【具体怎么用还得看应用场景和所选芯片】。

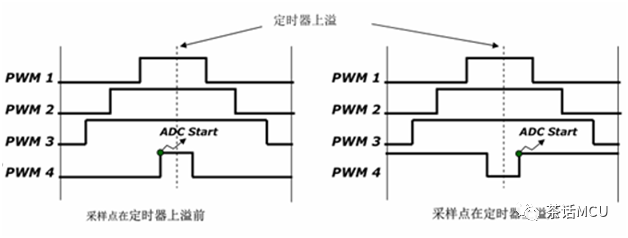

如上图所示,计数器工作在中心对齐计数模式。我们有时可能需要在计数器上溢点的左侧或右侧启动ADC转换,这时就可以针对性选择合适的中心对齐模式在合适的时间点开启ADC转换。

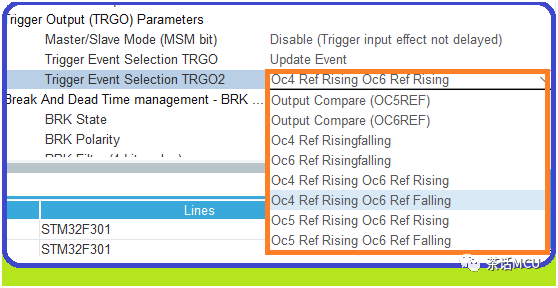

当然,单就上面提到的这点应用,STM32家族中的很多系列开辟了更为灵活方便且高效的硬件措施,比方STM32F3、STM32G4、STM32F7、STM32H7等系列,通过配置高级定时器通道4/5/6的输出信号的上升/下降沿及不同组合实现对ADC的同步触发,最大程度地减少软件处理和CPU参与。

下图是来自STM32F3系列TIM1的触发输出信号配置图。TRGO2事件可以作为ADC的触发事件,可选择单个事件或组合事件。【配置工具使用的STM32CubeMx】

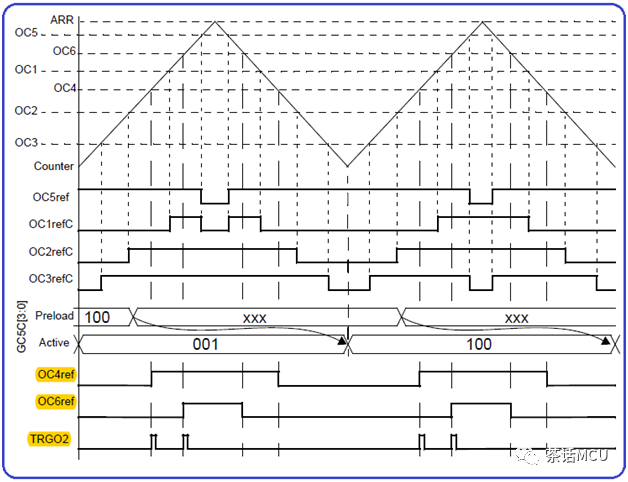

下面截图来自STM32F3系列参考手册定时器介绍章节,下图信息量很大,只是部分信息跟上面内容有关,贴到这里也算抛砖引玉。

这里重点旨在分享关于STM32定时器中心对齐计数三种模式的特征与彼此间的差异,知道这些特性后在需要的时候我们可以灵活运用。

我要赚赏金

我要赚赏金