电源完整性仿真

在电源完整性分析中,主要仿真类型有 直流压降分析、去耦分析和噪声分析。

直流压降分析包括对PCB上复杂走线和平面形状的分析,可用于确定由于铜的电阻将损失多少电压。

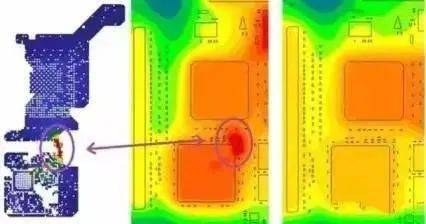

此外,还可以使用直流压降分析来确定高电流密度区域。实际上,可以使用热仿真器对它们进行协同仿真,以查看热效应。幸运的是,针对直流压降问题的解决方案非常简单:添加更多的金属。

这些额外金属可能会采用更宽和/或更厚的走线和平面形状、额外平面或额外过孔。

图3:显示PI/热协同仿真中“热点”的电流密度和温度图

上面简要讨论的去耦分析旨在确定和最大限度减少电路板不同IC位置上电源与地面之间的阻抗。去耦分析通常会驱动PDN中所用电容器的值、类型和数量的变化。

因此,它需要包括寄生电感和电阻的电容器模型。它还会驱动电容器安装方式的变化和/或电路板叠层的变化,以满足低阻抗要求。

表1:信号完整性和电源完整性之间的差异

信号完整性和电源完整性的分析对于成功的高速数字设计来说是至关重要的。它们为需要进行哪些设计更改提供了有价值的见解。

此外,随着建模方法和计算能力的改善,如果能够同时仿真这两种类型的完整性,则会清楚地了解电路的实际行为、设计中真正存在的利润以及它们如何实现最佳可能性能。

信号完整性仿真

我们已经了解到信号完整性仿真重点分析有关高速信号的3个主要问题: 信号质量、串扰和时序。

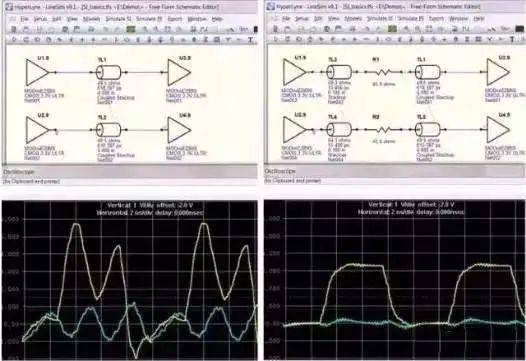

对于信号质量,目标是获取具有明确的边缘,且没有过度过冲和下冲的信号。

通常,可以通过添加某种类型的端接以使驱动器的阻抗与传输线的阻抗相匹配来解决这些问题。

对于多点分支总线,并非总能匹配阻抗,因此,需要将端接和拓扑的长度变化相结合来控制反射,使得它们不会对信号质量和时序产生不利影响。

图2:使用信号完整性分析和设计空间探索消除信号质量和串扰问题

可以运行这些相同的仿真,以确定信号经过电路板时的传输时间。电路板时序是系统时序的一个重要组成部分,并受线路长度、其在经过电路板时的传播速度以及接收器中波形形状的影响。

由于波形的形状确定了接收的信号穿越逻辑阈值的时间,因此,它对于时序来说是非常重要的。这些仿真通常会驱动走线长度约束的变化。

通常运行的另一个信号完整性仿真是串扰。

这涉及多条相互耦合的传输线。随着走线挤进密集的电路板设计,了解它们正在相互耦合多少能量对于消除因串扰产生的错误是非常重要的。

这些仿真将推动走线之间的最小间距要求。

我要赚赏金

我要赚赏金