Pblock是对一些逻辑实行物理上的约束,即把一些逻辑绑定到FPGA上固定的资源区域内。它是优化走线,改善时序的一种很重要方法。Pblock的大小限定了该逻辑单元使用的FPGA资源,pblock的位置限定了逻辑单元在FPGA中的位置。通常一个pblock大小不要超过总设计资源的20%。如果pblock占比资源很大,就要将一个pblock划分给更底层的逻辑。

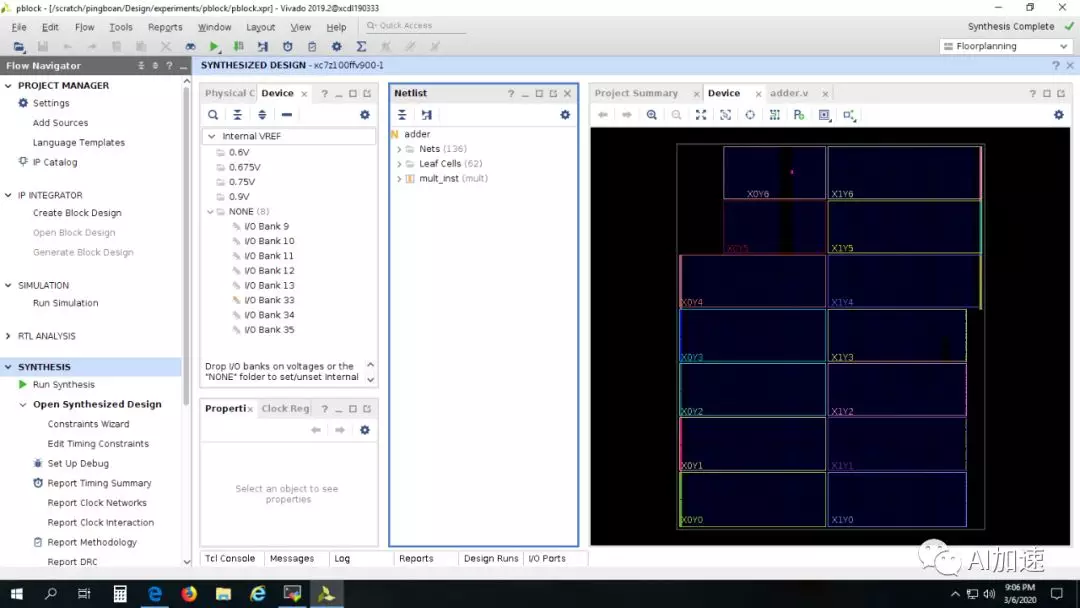

打开综合后的设计,我们切换到floorplanning选项,这个时候我们可以看到综合后的模块以及device视图。

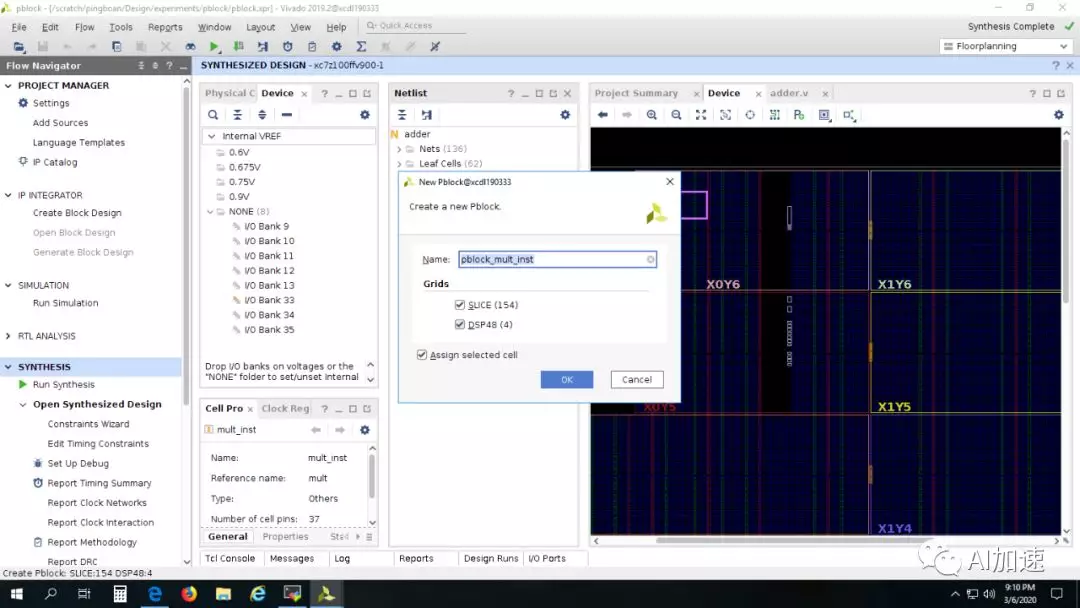

从netlist中可以看到有两个模块,一个是顶层模块adder,还有一个mult模块。我们选择mult模块,然后右键,floor planning/draw Pblock,我们就可以手动去画一个pblock。如下图所示,我们为pblock命名,然后可以看到其包含的资源:154个slice和4个DSP。

我们可以从pblock property中看到被分配为pblock的mult模块占用的资源:

我们放大device视图可以看到pblock的区域,其中含有两个矩形。外边矩形表示pblock覆盖的FPGA面积,内层矩形表明了这个pblock占用的FPGA资源。也就是我们的mult模块只能用内层矩形中的资源大小。

我们对手动生成的pblock进行保存,可以将tcl约束保存到xdc文件中。在xdc中的约束表示为:

这里用到了三个命令:

Create_pblock用于生成一个pblock。

Add_cells_to_Pblock用于将设计中模块添加到这个pblock中来。

Resize_pblock限定了pblock在FPGA中的位置。使用了slice的两个点来限制了pblock的位置,同时还给定了dsp的位置。

我要赚赏金

我要赚赏金