MRAM在读写方面可以实现高速化,这一点与静态随机存储器(SRAM)类似。由于磁体本质上是抗辐射的﹐MRAM芯片本身还具有极高的可靠性,即MRAM本身可以免受软错误之害。

MRAM可以做到与动态随机存储器(DRAM)类似的高密度,而且还具有读取无破坏性、无需消耗能量来进行刷新等优势,因为磁体没有漏电(leakage)之说。MRAM 与闪存(FLASH)同样是非易失性的,它还具备了写入和读取速度相同的优点,并具有承受无限多次读一写循环的能力。(在自由磁体层中来回切换的运动是电子的自旋,而电子本身永远不会磨损)。

MRAM另外一个吸引人的特色是,MRAM单元可以方便地嵌入到逻辑电路芯片中,这只需在后端的金属化过程增加一两步需要光刻掩模板的工艺即可。另外因为MRAM单元可以完全制作在芯片的金属层中,将2~3层单元叠放起来是可以实现的,这样就可以在逻辑电路上方构造规模极大的内存阵列。这样的可能性使我们可以预见到未来有望出现新型的、功能大大提升的单芯片系统这一美好前景。

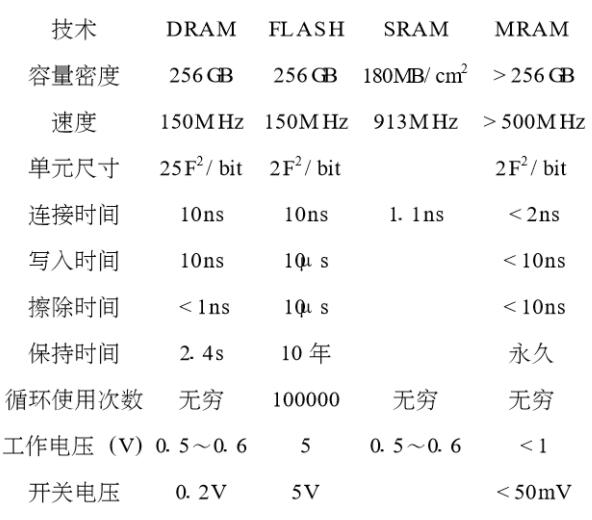

MRAM与现行各类存储器的比较

MRAM技术目前还存在一些困难,至少还没有一种实用化的、可靠的方式来实现大容量的MRAM。困难之一是对自由层进行写入(使磁矩平行或反平行底层)时所需的功率过高,因此交叉点开关架构受到连带写入问题的困扰。虽然只有所选中的位单元会承受由同时沿着字线和位线流动的电流引起的强烈的激励磁场,但沿着其中任一根线上分布的所有其他的位单元也会承受一半的切换功率,因此它们被“半选中”。理论上“半选中”的磁场作用并未强到足以重新改变这些单元对准方向的地步,因此这些位应该毫不受影响。

但由于MRAM单元要构成大规模的阵列,在那些为数众多的“半选中”的单元中某一个单元的自由层要出现状态的随机翻转的几率还是很大的。原因就在于对写入线((字或位)线通电时,我们同时降低了这条线(位于其上方或下方)上的每个单元的状态翻转的切换势垒。而这个势垒对MRAM阵列中的任一自由板在某个范围内是随机的,也就是说它们没有共同的、固定的切换阈值。于是“半选中”的单元数量越多,其中某个单元的状态接近自身阈值而出现翻转的几率就越大。

要避免这个问题就需要对阵列的布局、内存单元的构造以及导线上的电流分布进行严格而一致性的控制﹐而这种控制通常是难以实现的,尤其是大的点阵更是如此。这种现象在电子学上称为串扰(Cross talk)。

为了实现高密度的MRAM,缩短记忆位间的间距是必要的;然而当记忆位间的间距缩短到一定程度时,相邻的记忆位在执行写入动作的情形下相当容易相互干扰。由于MRAM是利用磁场来写入数据,而杂散场(stray filed )会影响到邻近的位,故串扰问题是很难避免的。于是在实践中交叉点阵列间的尺寸长度不能超过一定的限度,这样单位面积上的单元数(密度)受到限制。虽然当前的半导体集成电路早已突破了这一尺寸极限值,但MRAM技术中如何突破有待时日。

我要赚赏金

我要赚赏金