目前主流的MRAM利用巨磁阻效应( GMR)和磁性隧道结(MTJ))的隧穿电阻效应来进行存储。以MTJ为例,其元胞结构包括自由层、隧道层和固定层3个层面(如图1所示)。自由层的磁场极化方向是可以改变的,而固定层的磁场方向是固定不变的,在电场作用下电子会隧穿绝缘层势垒而垂直穿过器件,电流可隧穿的程度及MTJ的电阻均由2个磁性层的相对磁化方向来确定3'。当自由层的磁场方向与固定层的磁场方向相同时,存储单元呈现低阻态“0”;当两者磁场方向相反时,存储单元呈现高阻态“1”。MRAM器件通过检测存储单元电阻的高低来判断所存储的数据是“0”还是“1”。

图1MTJ结构示意图

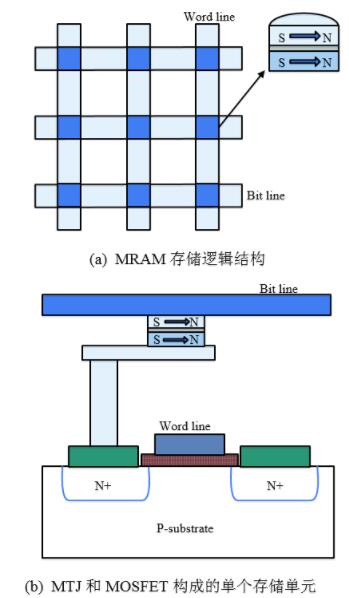

典型的存储单元电路结构如图2所示,一般是由1个NMOS管与MTJ单元集成在一起。NMOS管的栅极连接到存储阵列的字线( word line,WL)﹐源(漏)极通过源极线( source line, SL)与MTJ的固定层相连;而连接到MTJ自由层上的连线为存储阵列的位线( bit line, BL)。在位线和源极线之间施加不同的电压,产生流过磁隧道结的写入电流(Iwrite)﹐Iwrite可改变磁隧道结自由层的磁化方向,使隧穿电阻变化,完成“0”和“1”的存储。MRAM电路的读取机制是电流从位线流入,并通过MTJ和 MOS管输出,电压的大小同样依赖于MTJ电阻的高低,相同读取电流下所产生的输出电压不同。根据输出电压就可以判断存储单元所储存的数据是“0”还是“1”。

图2 MRAM工作原理示意图

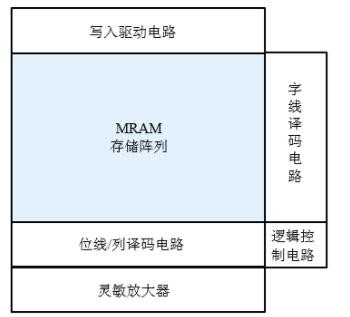

1个MTJ和1个MOSFET(即1T1M)结构构成MRAM基本的存储单元,众多存储单元又组成存储阵列,一般的MRAM电路除存储阵列之外还有相应的外围电路。如图3所示的存储器外围电路主要包括灵敏放大器、译码电路、读/写控制电路等。与SRAM等存储器类似,灵敏放大器主要用来对位线信号进行放大。可见除了存储阵列之外,外围电路均可采用与传统工艺兼容的CMOS电路进行设计制造。

图3典型存储单元结构示意图

我要赚赏金

我要赚赏金