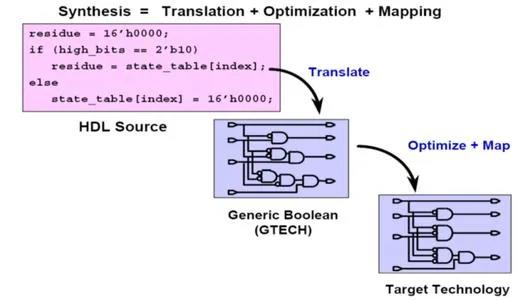

数字IC设计后端流程如上图所示,主要是以下步骤: 1.逻辑综合是将RTL代码映射为与工艺库相关的网表,该流程可放前端实现。逻辑综合中整个代码编译过程是在人为设定的约束条件下进行,通过约束和设定目标来指导工具完成Compiler的工作。逻辑综合过程可以看成一个多目标(频率、面积、功耗)多约束的工程优化问题。输出的网表主要用于P&R等流程。

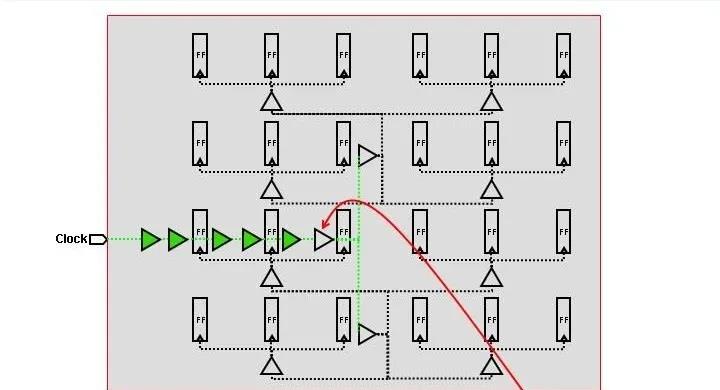

数字IC设计后端流程如上图所示,主要是以下步骤: 1.逻辑综合是将RTL代码映射为与工艺库相关的网表,该流程可放前端实现。逻辑综合中整个代码编译过程是在人为设定的约束条件下进行,通过约束和设定目标来指导工具完成Compiler的工作。逻辑综合过程可以看成一个多目标(频率、面积、功耗)多约束的工程优化问题。输出的网表主要用于P&R等流程。 2.DFT(Design ForTest,可测性设计)是在芯片内部加入可测试电路,它可让内部信号暴露给外部,其目的是方便芯片流片后测试。常见的DFT技术有扫描测试(SCAN)、边界扫描测试(BSCAN)、内建自测试(BIST)、静态电流(IDDQ)测试等。SCAN设计是将非扫描单元(如普通寄存器)替换成可扫描单元,然后再把它们连接成扫描链;BSCAN测试目标通常是IO-PAD,常用于板级、系统级追踪调试;BIST典型的应用是memory测试,也就是MBIST。 DFT一般有专门的部分负责,DFT设计完成后将正式进入后端设计流程。 3.数据导入。后端设计所需的设计数据主要包括前端设计后经过综合生成的门级网表、具有时序约束和时钟定义的SDC约束文件、物理设计单元库数据。 4.布局规划( Floorplan ) 。该阶段完成设计中IO Pad、宏单元的物理布局、标准单元布局约束和电源网络布局实现。IO Pad预先留出位置,而宏单元则主要根据时序要求进行摆放,标准单元则定义特定的区域范围由工具根据布局约束信息自动摆放,电源网络布局完成芯片工作时所需要的合理供电网络。 5.单元放置( Placement )。布局规划后,宏单元、IO Pad的位置和放置标准单元的约束区域都已确定,APR工具根据网表和时序约束信息进行自动放置标准单元工作。 6.时钟树综合( Clock Tree Synthesis )。该阶段用于实现芯片中的时钟树。芯片中的时钟需要驱动设计中所有的时序单元,时钟网络及其使用的缓冲器构成了物理上的时钟树。

2.DFT(Design ForTest,可测性设计)是在芯片内部加入可测试电路,它可让内部信号暴露给外部,其目的是方便芯片流片后测试。常见的DFT技术有扫描测试(SCAN)、边界扫描测试(BSCAN)、内建自测试(BIST)、静态电流(IDDQ)测试等。SCAN设计是将非扫描单元(如普通寄存器)替换成可扫描单元,然后再把它们连接成扫描链;BSCAN测试目标通常是IO-PAD,常用于板级、系统级追踪调试;BIST典型的应用是memory测试,也就是MBIST。 DFT一般有专门的部分负责,DFT设计完成后将正式进入后端设计流程。 3.数据导入。后端设计所需的设计数据主要包括前端设计后经过综合生成的门级网表、具有时序约束和时钟定义的SDC约束文件、物理设计单元库数据。 4.布局规划( Floorplan ) 。该阶段完成设计中IO Pad、宏单元的物理布局、标准单元布局约束和电源网络布局实现。IO Pad预先留出位置,而宏单元则主要根据时序要求进行摆放,标准单元则定义特定的区域范围由工具根据布局约束信息自动摆放,电源网络布局完成芯片工作时所需要的合理供电网络。 5.单元放置( Placement )。布局规划后,宏单元、IO Pad的位置和放置标准单元的约束区域都已确定,APR工具根据网表和时序约束信息进行自动放置标准单元工作。 6.时钟树综合( Clock Tree Synthesis )。该阶段用于实现芯片中的时钟树。芯片中的时钟需要驱动设计中所有的时序单元,时钟网络及其使用的缓冲器构成了物理上的时钟树。 7.全局与细节布线( Global&Detail Route)。布线是指在满足工艺规则和布线层数限制、线宽、线间距限制和各线网可靠绝缘的电性能约束的条件下,根据电路的连接关系将各单元模块的输入输出端口用互连线连接起来。 8.电压衰减分析( IR-drop&EM )。布线完成后,设计数据就基本确定了,对整个设计进行功耗及电压降分析就更加精确,因此通过电压降分析评估电源网络是否达到设计要求。 9.时序验证与ECO。后端一般是通过静态时序分析来验证系统是否满足时序要求。ECO(工程修改,Engineering Change Order)是对电路和单元布局进行小范围改动,不用重新布局布线,通过手工修改版图来满足功能和时序要求或修复一些bug,避免重复整个芯片的设计过程。 10.功能等价性检查。布局布线过程需要根据物理情况修改门级网表,所以通过等价性检查这个过程来确认最终的网表与前端提供的初始网表功能上是否一致。 11.物理验证。物理验证中主要包括DRC和LVS两大部分, DRC是对芯片版图中的各层物理图形进行设计规则检查,保证满足流片要求。LVS保证物理验证流片出来的物理版图和实际设计的电路图一致。 12.Signoff,后端所说的signoff,是指将设计数据交给芯片制造厂商生产之前,对设计数据进行复检,确认设计数据达到交付标准,这些检查和确认统称为signoff。例如timing signoff 和 physical signoff。 13.流片(Tapeout )。在所有检查和验证都准确无误的情况下,把最终的版图GDSII文件传递给流片厂进行掩膜制造。 IC后端设计工具介绍: 数字后端设计中常用的工具主要由Cadence, Synopsys和Mentor三大公司推出。 逻辑综合工具:Synopsys DC ,Cadence Genus 可测性设计工具:Mentor系列DFT工具,Synopsys DFT Compiler 布局布线工具:Cadence Innovus ,Synopsys ICC2 静态时序分析工具:PrimeTime,Encounter Timing System 功耗分析工具:RedHawk,PrimeRail,Encounter Power System 形式化验证工具:Formality,Conformal 寄生参数提取工具:QRC Extraction,Star-RCXT,Calibre xRC 物理验证工具:Calibre,Hercules

7.全局与细节布线( Global&Detail Route)。布线是指在满足工艺规则和布线层数限制、线宽、线间距限制和各线网可靠绝缘的电性能约束的条件下,根据电路的连接关系将各单元模块的输入输出端口用互连线连接起来。 8.电压衰减分析( IR-drop&EM )。布线完成后,设计数据就基本确定了,对整个设计进行功耗及电压降分析就更加精确,因此通过电压降分析评估电源网络是否达到设计要求。 9.时序验证与ECO。后端一般是通过静态时序分析来验证系统是否满足时序要求。ECO(工程修改,Engineering Change Order)是对电路和单元布局进行小范围改动,不用重新布局布线,通过手工修改版图来满足功能和时序要求或修复一些bug,避免重复整个芯片的设计过程。 10.功能等价性检查。布局布线过程需要根据物理情况修改门级网表,所以通过等价性检查这个过程来确认最终的网表与前端提供的初始网表功能上是否一致。 11.物理验证。物理验证中主要包括DRC和LVS两大部分, DRC是对芯片版图中的各层物理图形进行设计规则检查,保证满足流片要求。LVS保证物理验证流片出来的物理版图和实际设计的电路图一致。 12.Signoff,后端所说的signoff,是指将设计数据交给芯片制造厂商生产之前,对设计数据进行复检,确认设计数据达到交付标准,这些检查和确认统称为signoff。例如timing signoff 和 physical signoff。 13.流片(Tapeout )。在所有检查和验证都准确无误的情况下,把最终的版图GDSII文件传递给流片厂进行掩膜制造。 IC后端设计工具介绍: 数字后端设计中常用的工具主要由Cadence, Synopsys和Mentor三大公司推出。 逻辑综合工具:Synopsys DC ,Cadence Genus 可测性设计工具:Mentor系列DFT工具,Synopsys DFT Compiler 布局布线工具:Cadence Innovus ,Synopsys ICC2 静态时序分析工具:PrimeTime,Encounter Timing System 功耗分析工具:RedHawk,PrimeRail,Encounter Power System 形式化验证工具:Formality,Conformal 寄生参数提取工具:QRC Extraction,Star-RCXT,Calibre xRC 物理验证工具:Calibre,Hercules

我要赚赏金

我要赚赏金