由于闪存的成本取决于其裸片面积,如果可以在同样的面积上存储更多数据,闪存将更具成本效益。NAND闪存有三种主要类型:单层单元(SLC)、多层单元(MLC)和三层单元(TLC)。顾名思义,在相同的单位面积上,TLC闪存比MLC存储的数据更多,而MLC又比SLC存储的数据多。另一种新型的NAND闪存称为3DNAND或V-NAND(垂直NAND)。通过在同一晶圆上垂直堆叠多层存储单元,这种类型的闪存可以获得更大的密度。

浮栅晶体管

闪存将信息存储在由浮栅晶体管组成的存储单元中。为了更好地理解不同类型的NAND闪存,让我们来看看浮栅晶体管的结构、工作原理及其局限。

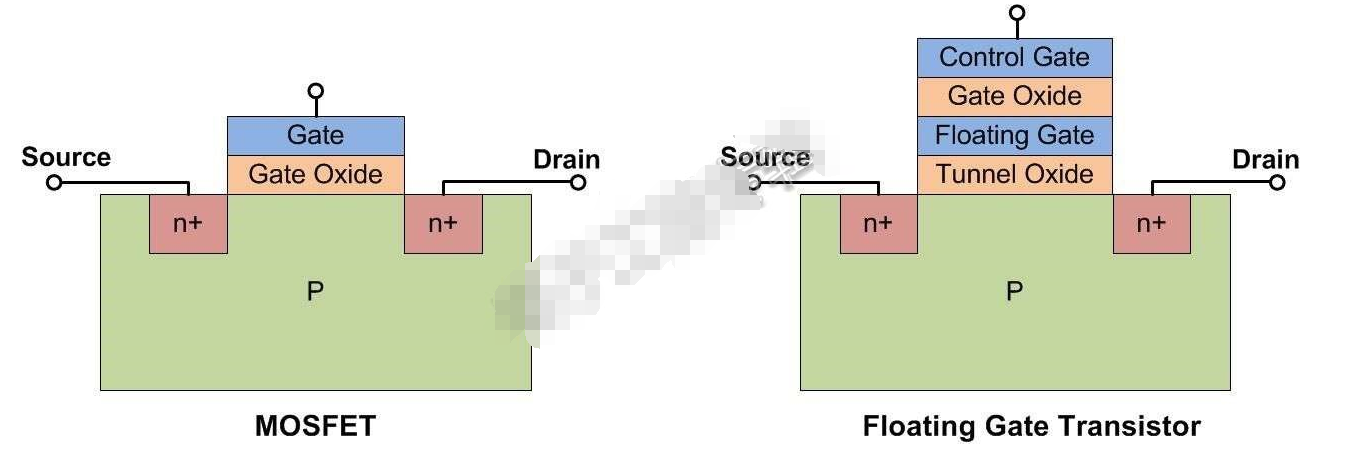

浮栅晶体管或浮栅MOSFET(FGMOS)跟常规MOSFET非常类似,有一点不同的是它在栅极和沟道之间添加了额外的电绝缘浮栅。

图1:浮栅MOSFET(FGMOS)与常规MOSFET对比。

由于浮栅是电隔离的,所以即使在去除电压之后,到达栅极的任何电子也会被捕获。这使得存储器具有非易失性。与具有固定阈值电压的常规MOSFET不同,FGMOS的阈值电压取决于存储在浮栅中的电荷量。电荷越多,阈值电压越高。与常规MOSFET类似,当施加到控制栅极的电压高于阈值电压时,FGMOS将开始导通。因此,通过测量其阈值电压并与固定电压电平进行比较,就可以识别存储在FGMOS中的信息。这称为闪存的读操作。

可以使用两种方法将电子放置在浮栅中:Fowler-Nordheim隧穿或热载流子注入。对于Fowler-Nordheim隧穿,在带负电的源极和带正电的控制栅极之间施加强电场。这使得来自源极的电子隧穿穿过薄氧化层并到达浮栅。隧穿所需的电压取决于隧道氧化层的厚度。对于热载流子注入方法,高电流通过沟道,为电子提供足够的能量以穿过氧化物层并到达浮栅。

通过在控制栅极上施加强负电压,并在源极和漏极端子上施加强正电压,使用Fowler-Nordheim隧穿可以从浮栅移除电子。这将导致被捕获的电子通过薄氧化层返回沟道。在闪存中,将电子放置在浮栅中被认为是编程/写入操作,而去除电子被认为是擦除操作。

隧穿工艺有一个主要缺点:它会逐渐损坏氧化层。这被称为闪存磨损。每次对单元进行编程或擦除时,一些电子都会粘在氧化层中,从而逐渐磨损氧化层。一旦氧化层达到不再能够可靠地区分编程和擦除状态时,这一单元就被认为是坏的或磨损的。由于读取操作不需要隧穿,它们不会磨损单元。因此,闪存的寿命表示为它可以支持的编程/擦除(P/E)周期数。有一篇名为“了解典型和最大编程/擦除性能”的文章解释了如何获得编程和擦除性能的典型值和最大值。

SLCNAND闪存

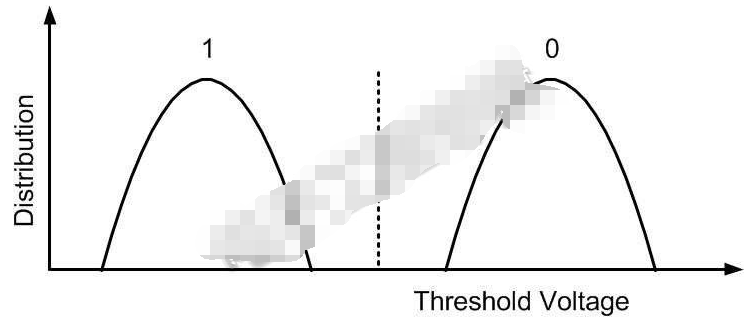

在SLC闪存中,每个存储单元仅存储一位信息:逻辑0或逻辑1。单元的阈值电压与某个电压电平进行比较,如果高于这一电平,则该位被视为逻辑0。如果低于这一电平则为逻辑1。

图2:将SLC闪存单元中的电压与阈值电压进行比较,以确定它是逻辑0(高于阈值)还是逻辑1(低于阈值)。

由于只有两个电平,因此两个电平电压之间的电压差距可能非常高。这使得读取存储单元更容易,更快捷。原始误码率(RBER)也很低,这要归功于较大的电压差,因为在读取操作期间任何泄漏或干扰的影响较小。低RBER还减少了特定数据块所需的ECC位数。

大电压差的另一个优点是磨损的影响相对较小,因为微小的电荷泄漏具有相对较低的影响。逻辑电平的更宽分布也有助于以更低的电压对存储单元进行编程或擦除,这进一步增加了单元的耐用性,进而提高了寿命周期内P/E循环数。

但是SLC闪存也有缺点,与其他类型的闪存相比,它在相同裸片面积上可以存储的数据要少,因此其存储单元的成本更高。SLC闪存通常用于对成本不敏感且需要高可靠性和耐用性的应用中,例如对P/E循环数有很高要求的工业和企业级应用。

MLCNAND闪存

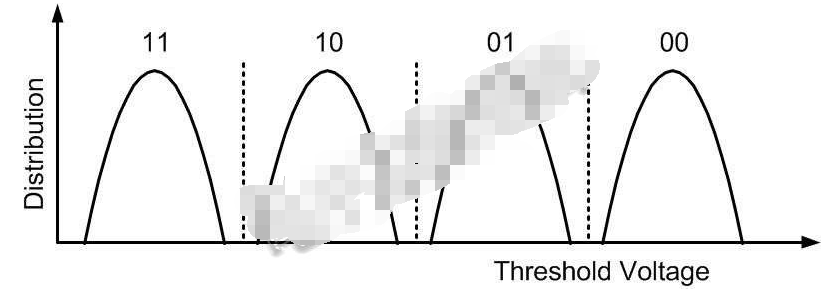

在MLC闪存中,每个单元存储两位信息,即00、01、10和11。在这种情况下,阈值电压要与三个电平进行比较(总共4个电压带)。

图3:将MLC闪存单元中的电压与三个阈值电压进行比较,以确定其两位逻辑值。

因为要对多个电平进行比较,读取操作需要更加精确,导致其读取速度比SLC闪存更慢。由于较低的电压差,原始误码率(RBER)也相对较高,而且特定数据块需要更多的ECC比特位。现在磨损的影响也更为显着,因为与SLC闪存相比,任何电荷泄漏都会产生更大的相对影响,从而减少了寿命周期内P/E循环次数。

由于需要仔细编程以便将电荷存储在每个逻辑电平所需的紧密窗口内,MLC闪存的编程操作也要慢得多。然而,它的主要优点是每比特成本更低,要比SLC闪存低2-4倍。MLC闪存通常用于对成本更敏感的应用,例如消费电子或游戏机,因为这类应用对性能、可靠性和耐用性的要求不是那么严格,并且所要求的寿命周期内P/E循环次数也相对较低。有一篇题为“SLCVS.MLCNAND闪存”的文章提供了SLC和MLC闪存的详细比较。

企业级eMLCNAND闪存

MLC闪存的低可靠性和耐用性使得它不适合企业级应用,而低成本是它得以存在的主要因素。为了发挥其低成本优势,闪存制造商开发出一种优化级别的MLC闪存,称为eMLC,它具有较高的可靠性和耐用性。eMLC中的数据密度通常会降低,从而提供更好的电压差以提高可靠性。较慢的擦除和编程循环通常用于减少磨损的影响并提高耐用性。还有许多其他技巧可以提高eMLC的可靠性和耐用性,每家制造商各有自己的方法。

TLCNAND闪存

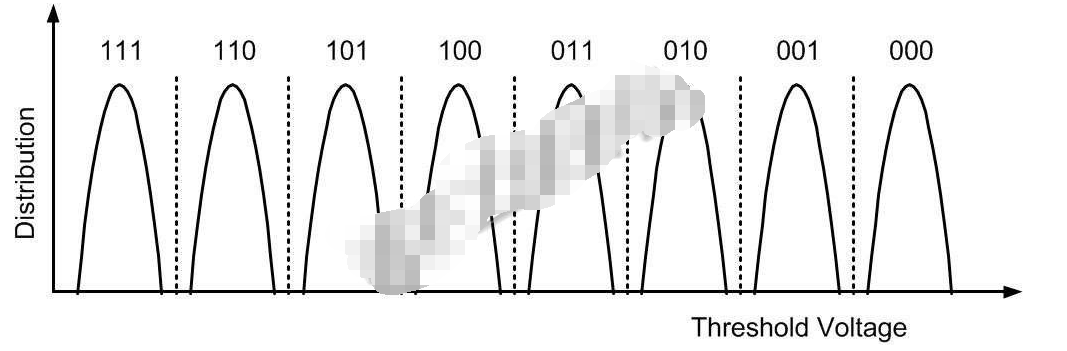

在TLC闪存中,每个单元存储3位信息。现在是将阈值电压与七个电平(总共8个电压带)进行比较。

图4:将TLC闪存单元中的电压与七个阈值电压进行比较,以确定其三位逻辑值。

与SLC闪存相比,TLC闪存需要将更多电平进行比较,其读取操作需要高度精确,因此速度比较慢。原始误码率(RBER)也很高,这就需要为特定数据块提供更多ECC位。此外,其单元磨损的影响也增加了,大大减少了寿命周期内P/E循环次数。其编程操作也较慢,因为电压需要精确以便将电荷存储在每个逻辑电平所需的更严格的窗口内。

TLC闪存的主要优势是每比特的成本最低,要比SLC或MLC闪存都低得多。TLC闪存适用于对成本高度敏感而对P/E循环次数要求较低的应用,例如消费类电子产品。

SLC、MLC、eMLC和TLC的比较

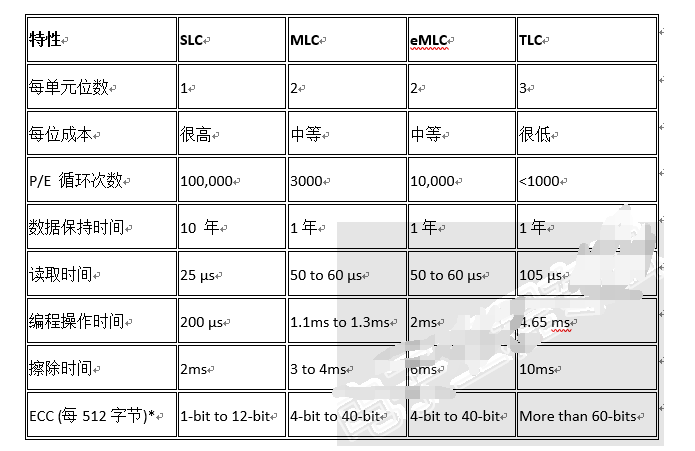

表1对比了不同类型闪存的主要参数,假设都采用类似的光刻工艺。这些值仅用于是性能对比,就特定存储器产品而言不一定准确。

表1:不同类型闪存的主要参数比较。

*ECC位数取决于工艺节点,较小的工艺节点需要更多的ECC位。

3DNAND闪存

上面讨论的所有不同类型的闪存都是二维的,意思是存储单元仅布置在晶圆的X-Y平面上。使用2D闪存技术,要在同一个晶圆中实现更高密度的唯一方法是缩小光刻工艺。其缺点是,对于较小的光刻节点,NAND闪存中的错误更为频繁。另外,可用的最小光刻节点也是有下限的。

为了提高存储密度,制造商开发了3DNAND或V-NAND(垂直NAND)技术,它可将Z平面中的存储单元堆叠在同一晶圆上。以这种方式构建存储单元有助于在相同的裸片面积上实现更高的存储密度。在3DNAND闪存中,存储单元是作为竖直串连接的,而不是2DNAND中的水平串。

第一批3D闪存产品有24层。随着这一技术的进步,已经可以制造出32、48、64甚至96层的3D闪存。其优势在于同一区域中的存储单元数量明显增加。这也使存储器制造商能够使用更大的光刻工艺来制造更可靠的闪存芯片。

在3D闪存中可以看到另一个主要的技术转变,就是使用电荷陷阱而不是浮栅晶体管。电荷陷阱在结构上类似于FGMOS,只是用氮化硅膜代替了浮栅。请注意,由于大规模制造的困难,电荷陷阱在市场上还没有被广泛使用。生产3D闪存时,由于难以使用浮栅晶体管来构造垂直串,电荷陷阱技术便被引进,它也有其他一些固有的优点。

与FGMOS相比,基于电荷陷阱的存储器有许多优点。它可以在较低电压下编程和擦除,从而大大提高耐用性。由于捕获层(氮化物)是绝缘层,电荷不会泄漏,因而也提高了可靠性。由于电荷不会从电荷陷阱的一侧流到另一侧,因此可以在同一陷阱层上存储多于一位的电荷。赛普拉斯(前Spansion)已经在NOR闪存中有效地利用了这种特性,称为MirrorBit技术,它可将两位数据存储在一个存储单元中,类似于MLC闪存。

未来的趋势

所有主要的闪存制造商都在积极致力于采用不同的方法,以降低每比特闪存的成本,同时继续生产适用于各种应用的存储器产品。业界正在积极研究如何增加3DNAND闪存中垂直层的数量。虽然15nm工艺似乎是目前NAND闪存中最小的工艺节点,但缩小闪存的光刻节点的努力仍在继续。将MLC和TLC技术与3DNAND闪存相结合也正在积极探索中,许多制造商已经取得了成功。随着新技术的出现,我们可能很快就会看到存储单元可以存储一个字节(8位)的数据,垂直层将达到256层甚至更高。

我要赚赏金

我要赚赏金