本文将谈一谈使用有刷直流电机驱动器IC进行PWM驱动时,通过输出MOSFET的寄生二极管进行电流再生时的功耗。之所以讨论这个话题,是因为再生时的实际功耗可能会大于估算值,在某些情况下可能会引发问题,所以需要注意。

通过MOSFET的寄生二极管进行电流再生时,功耗是否会大于计算值?当通过输出MOSFET的寄生二极管进行电流再生时,其功耗应该是寄生二极管的正向电压×电机电流。然而实际上,有时功耗可能会大于这个计算值。

其原因是当电流流过输出MOSFET的寄生二极管从而产生正向电压时,MOSFET结构上固有的寄生晶体管会工作,电流从电源流向GND。这个电流小到不足流过二极管的电流的几十分之一,但功耗是“电源电压×电源-GND间电流”,是电源电压较高时不可忽视的值。

下面将从驱动器输出MOSFET的状态、电流的流动以及输出MOSFET的结构角度来解释说明这种现象。

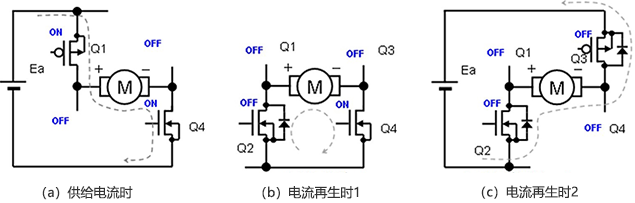

首先来看电流再生时输出MOSFET的状态和再生电流的流动情况。下面是H桥电路,但其中省略了与工作无关的MOSFET。(a)是给电机供给电流时的电路,(b)和(c)都是电流再生时的电路,但由于有两种电路状态,所以将(b)命名为“电流再生时1”、将(c)命名为“电流再生时2”。

(b)电流再生时1是在供给电流时将导通的Q1关闭、而Q4保持导通。在这种状态下,电流通过关断状态的Q2的寄生二极管和导通状态的Q4再生。

(c)电流再生时2是在供给电流时将导通的Q1和Q4关断,所有MOSFET处于关断状态。在这种情况下,电流通过Q2和Q4的寄生二极管再生。

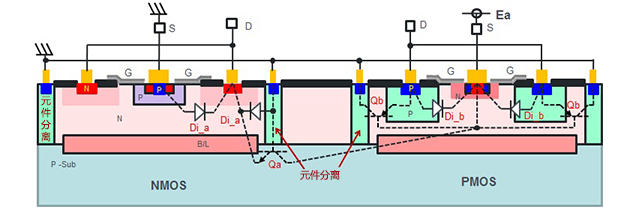

接下来,为了说明导致流过附加电流的寄生晶体管,给出了电机驱动器IC的输出MOSFET的结构示意图(截面图)。在上面的电路图中,高边使用了Pch MOSFET,低边使用了Nch MOSFET,所以下图中也分别列出了它们的结构。

在输出Nch MOSFET中,由漏极D的N型扩散层、元件分离用的P型扩散层和连接到电源的N型扩散层(在这里是连接到输出Pch MOSFET的源极S),可以形成寄生NPN晶体管Qa。

当再生电流流过这个Nch MOSFET的源极和漏极之间的寄生二极管Di_a时,由于元件分离P型扩散层是与GND相连接的,因此寄生NPN晶体管Qa的基极和****极之间的二极管也会产生正向电压。为此,寄生NPN晶体管Qa导通,流过集电极电流并从电源Ea汲取电流。

对于输出Pch MOSFET来说,原理也相同。可以由漏极D的P型扩散层、与源极S共用的背栅N型扩散层、元件分离等的P型扩散层来形成寄生PNP晶体管Qb。

当再生电流流过该Pch MOSFET的源极和漏极之间的寄生二极管Di_b时,寄生PNP晶体管Qb导通,流过集电极电流,且电流流向GND。

当再生电流流过输出MOSFET的寄生二极管时,电流通过寄生晶体管在电源和GND之间流动。一般来讲,流过的电流比再生电流小两个数量级左右,但会因IC所使用的工艺和MOSFET的布局而有很大差异。因此,当通过输出MOSFET的寄生二极管使用电流再生时,需要确认通过这些寄生晶体管流过的电流大小。

例如,在“(c)电流再生时2”中,假设电源电压Ea=24V,再生电流Io=1.0A,Nch MOSFET寄生二极管的正向电压VF_N=0.8V,Pch MOSFET的寄生二极管正向电压VF_P=0.95V,Nch MOSFET的寄生晶体管和Pch MOSFET的寄生晶体管的电源和GND之间流动的电流与再生电流之比都为k1=1/100,则功耗Pc如下:

Pc=Io×(VF_N+VF_P+2×k1×Ea) =1×(0.8+0.95+2×1/100×24)=1.75+0.48=2.23W

在这个示例中,流经寄生晶体管的电流对功耗的影响是绝对不能忽视的。在电源电压Ea高时需要注意。

我要赚赏金

我要赚赏金